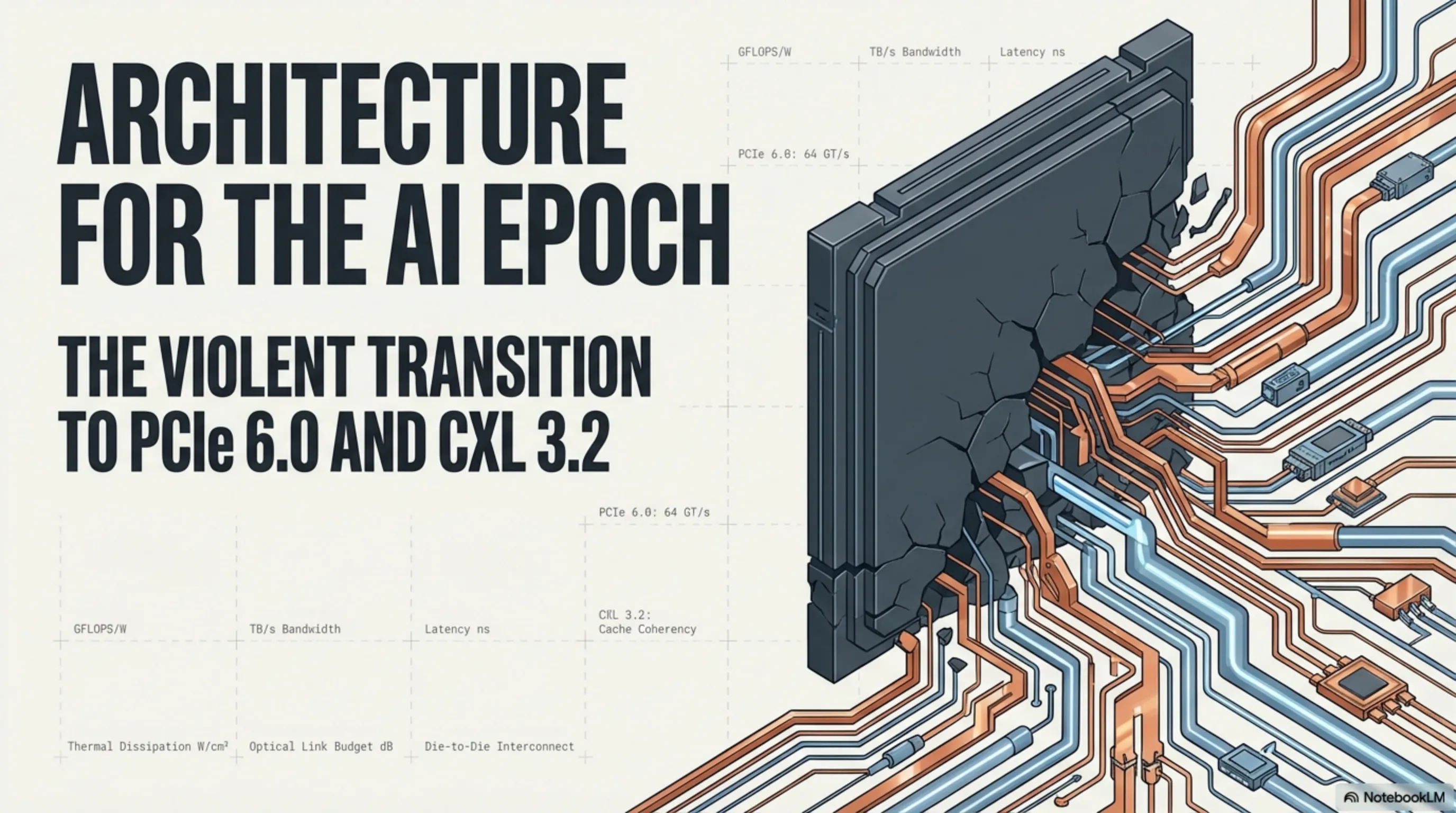

تحلیل جامع مهاجرت صنعتی به استاندارد PCIe 6.0 و پروتکل CXL 3.2 در سال ۲۰۲۶ برای مقابله با گلوگاههای داده در عصر هوش مصنوعی. ما در این مقاله به بررسی تکنولوژی سیگنالینگ PAM4، واحد اصلاح خطای FEC و انقلاب "تجزیهپذیری حافظه" میپردازیم. همچنین نقش کلیدی تراشههای Retimer در پایداری شبکه و تأثیر این زیرساختهای جدید بر دیتاسنترهای مدرن خاورمیانه و مدلهای زبانی بزرگ (LLM) مورد بحث قرار میگیرد.

بخش اول: مقدمه و پایان سلطنت کوتاه PCIe Gen 5

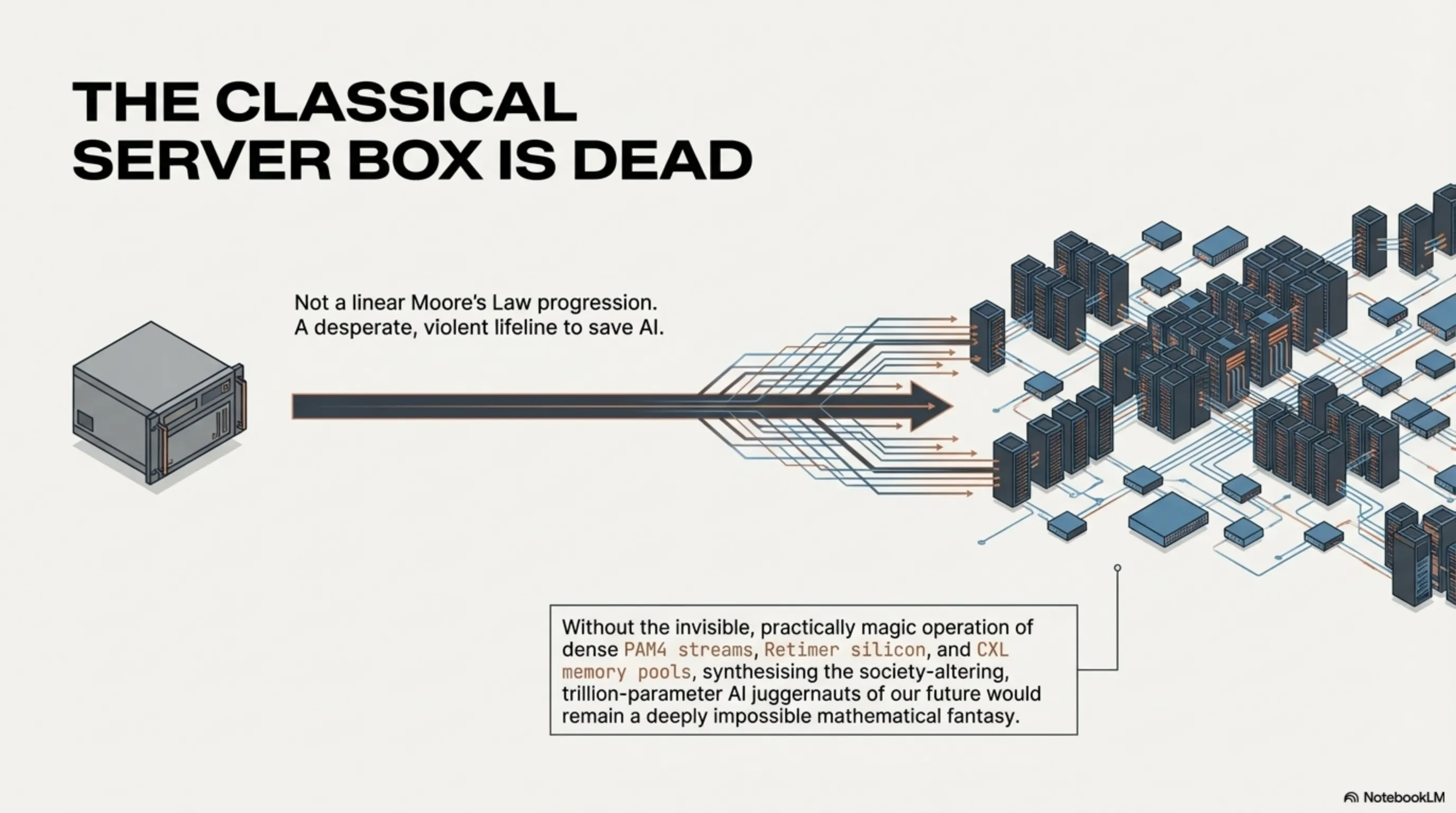

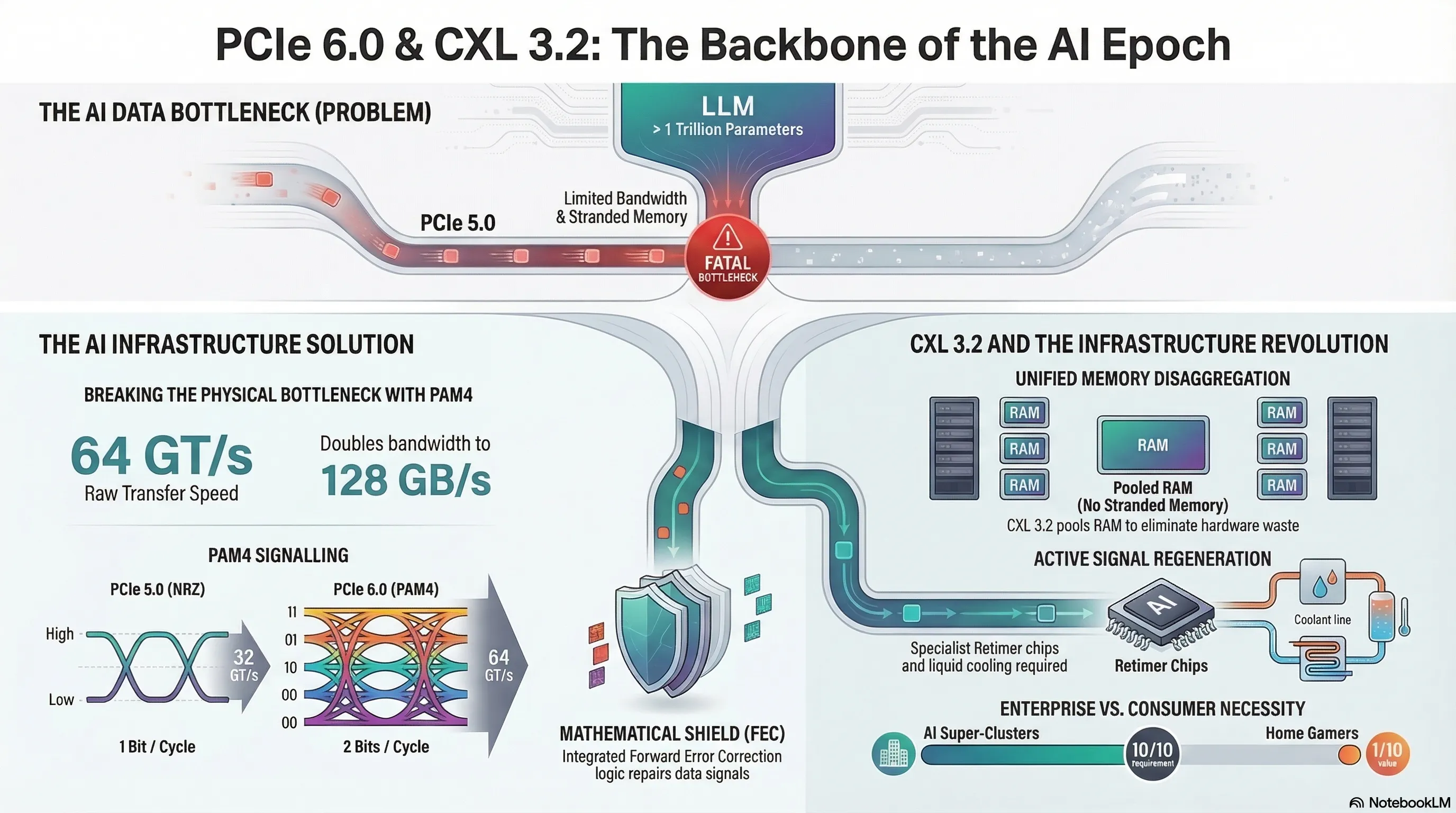

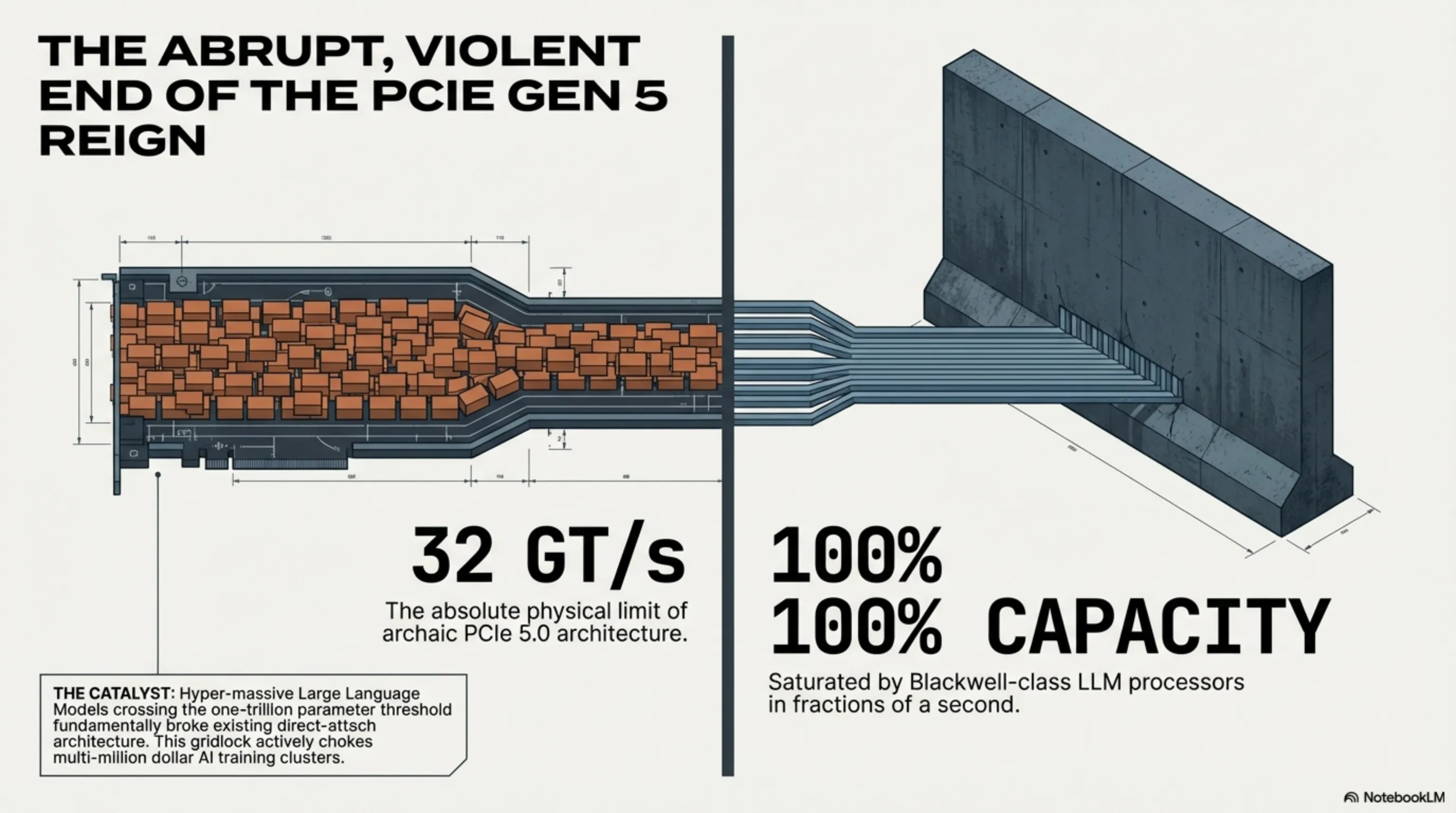

در اواسط سال ۲۰۲۴ و آغاز سال ۲۰۲۵، رونمایی از پردازندههای سرور مجهز به گذرگاه PCIe 5.0 یک دستاورد عظیم به شمار میرفت. دوبرابر شدن پهنای باند از PCIe 4.0 به نظر میرسید که برای سالها نیازهای انتقال داده در سرورها را تامین خواهد کرد. با این حال، با انفجار بیسابقه مدلهای زبانی بزرگ (LLMs) و نیاز به پردازش گرافیکی فوقسنگین در سالهای ۲۰۲۵ و ۲۰۲۶، طراحان سیلیکون در شرکتهایی مانند انویدیا و AMD با یک حقیقت هولناک مواجه شدند: حتی گذرگاه ۳۲ گیگاترانسفر در ثانیه (GT/s) نیز در حال تبدیل شدن به یک گلوگاه مرگبار (Bottleneck) برای خوشههای هوش مصنوعی بود.

کارتهای گرافیک قدرتمندی نظیر سری Blackwell انویدیا (که خبر توقف فروش H200 آنها در چین به تازگی بازار را شوکه کرد) با سرعتی باورنکردنی دیتا را میبلعند. این پردازندهها چنان قدرتمند هستند که در حین لود کردن مدلهای چندهزار میلیارد پارامتری، تمام لاینهای PCIe 5.0 مادربردِ سرور را در کسر از ثانیه به حالت اشباع ۱۰۰ درصدی میرسانند. در بهار ۲۰۲۶، پاسخ رسمی صعنت سرور به این بحران فیزیکی، آغاز عملیاتیِ مهاجرت به استاندارد PCIe Gen 6.0 است؛ استانداردی که نه تنها سرعت را به ۶۴ گیگاترانسفر بر ثانیه دو برابر میکند، بلکه معماریِ کاملاً متفاوتی برای انتقال جریان بیتها (Bit-stream) در روی بُردهای مدار چاپی معرفی مینماید.

بخش دوم: کالبدشکافی سیگنالینگ PAM4 در PCIe Gen 6.0

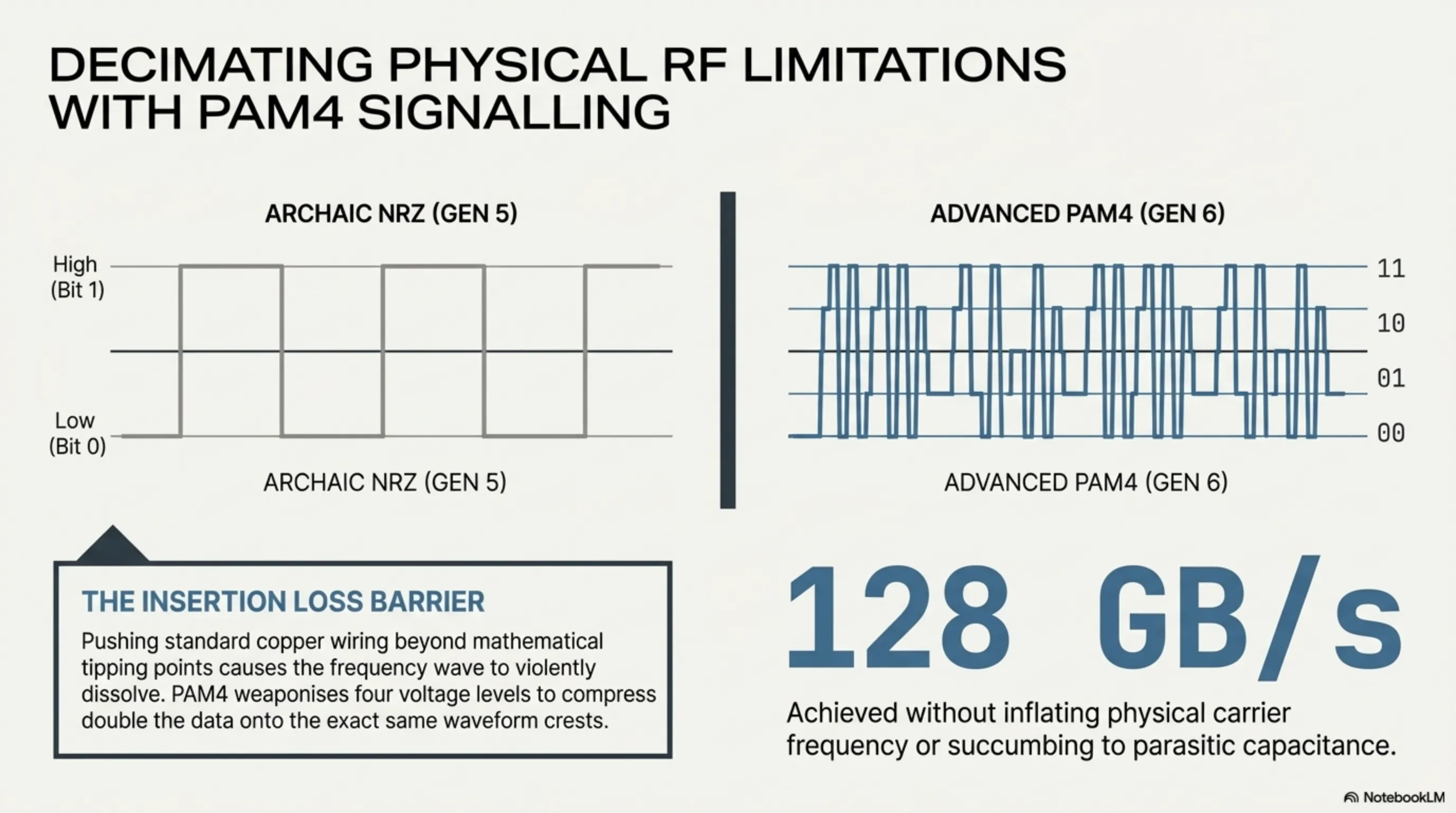

از زمان معرفی اولین نسخه PCIe در سال ۲۰۰۳ تا نسخه Gen 5، সমস্ত نسخهها از یک روش رمزگذاری سیگنال دیجیتال موسوم به NRZ (Non-Return-to-Zero) استفاده میکردند. در NRZ، ما فقط دو سطح ولتاژ داریم: ولتاژ بالا (که به عنوان بیت ۱ خوانده میشود) و ولتاژ پایین (که به عنوان بیت ۰ خوانده میشود). مشکل اینجا بود که فیزیک به ما اجازه نمیدهد فرکانس خامِل (Carrier Frequency) را تا بینهایت روی سیمهای مسی افزایش دهیم؛ زیرا افزایش بیش از حد فرکانس باعث ایجاد پدیده "از بین رفتن سیگنال" (Insertion Loss) در طول کابل و روی مادربرد میشود.

برای عبور از این محدودیت، مهندسان کنسرسیوم PCI-SIG برای طراحی PCIe 6.0 تصمیم گرفتند روش کهنه NRZ را به زبالهدان تاریخ بفرستند و معماری پیشرفته PAM4 (Pulse Amplitude Modulation 4-level) را مستقیماً روی خطوط ارتباطی سرورها پیاده کنند. PAM4 به جای دو سطح ولتاژ، از چهار سطح ولتاژ مجزا (00, 01, 10, 11) استفاده میکند. این تغییر بدان معناست که در هر تغییر سیگنال (Clock Cycle)، به جای یک بیت، دو بیت داده به صورت همزمان ارسال میشود.

به زبان ساده، PCIe 6.0 بدون اینکه فرکانس فیزیکی انتقال دیتا روی سیم مسی را نسبت به PCIe 5.0 وحشتناکتر کند، صرفاً با فشردهتر کردن اطلاعات روی موج، توانسته پهنای باند را به طور کامل دو برابر کند و به عدد خیرهکننده ۱۲۸ گیگابایت بر ثانیه (در یک اسلات x16 دورطرفه) برساند. این یک پیروزی مطلق مهندسی در برابر محدودیتهای مقاومت و خازن است.

بخش سوم: نقش حیاتی Forward Error Correction (FEC) در مهار خطای سیگنال

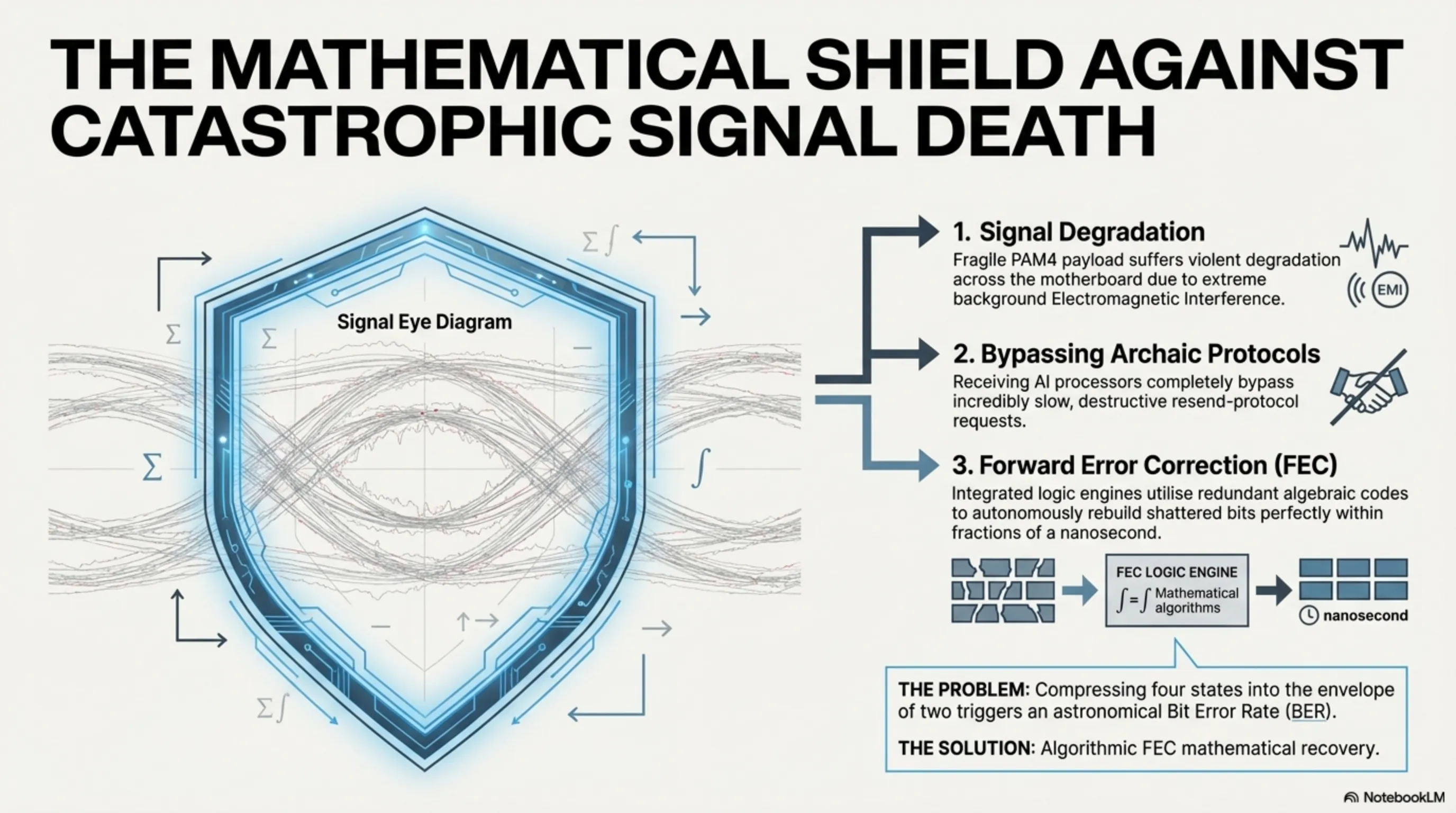

البته در دنیای مهندسی هیچچیز رایگان نیست. وقتی شما به جای دو سطح ولتاژ از چهار سطح ولتاژ استفاده میکنید، فاصلهی ولتاژی بین این سطوح بسیار کمتر (چشم دیاگرام بسیار کوچکتر) میشود. این مسئله باعث میشود سیگنالها به شدت به نویزهای الکترومغناطیسی حساس شوند و نرخ خطای بیت (Bit Error Rate - BER) به طرز وحشتناکی بالا برود؛ یعنی سرور دائماً دادهها را اشتباه میخواند!

برای جلوگیری از فروپاشی سیستم، استاندارد PCIe 6.0 برای اولین بار واحدی به نام Forward Error Correction (FEC) یا اصلاح خطای پیشرو را در لایه منطقی خود ادغام کرد. واحد FEC در کنار پکیجهای دیتا، کدها و الگوریتمهای بازیابی اطلاعات میفرستد. بنابراین، اگر به دلیل نویز چند بیت از بین بروند، پردازنده گیرنده به جای اینکه درخواستِ پرهزینه ارسال مجدد (Resend) کند، خودش با استفاده از فرمولهای ریاضی و کدهای FEC، بیتِ خراب شده را در کسری از نانوثانیه حدس زده و تعمیر میکند. ترکیب PAM4 به علاوه FEC، کلید واژههایی هستند که زیرساخت شبکه و انتقال دیتا را در دیتاسنترهای سال ۲۰۲۶ و ۲۰۲۷ زنده نگه داشتهاند.

بخش چهارم: انقلاب CXL 3.2: تجزیهپذیری حافظه (Memory Disaggregation) در دیتاسنترها

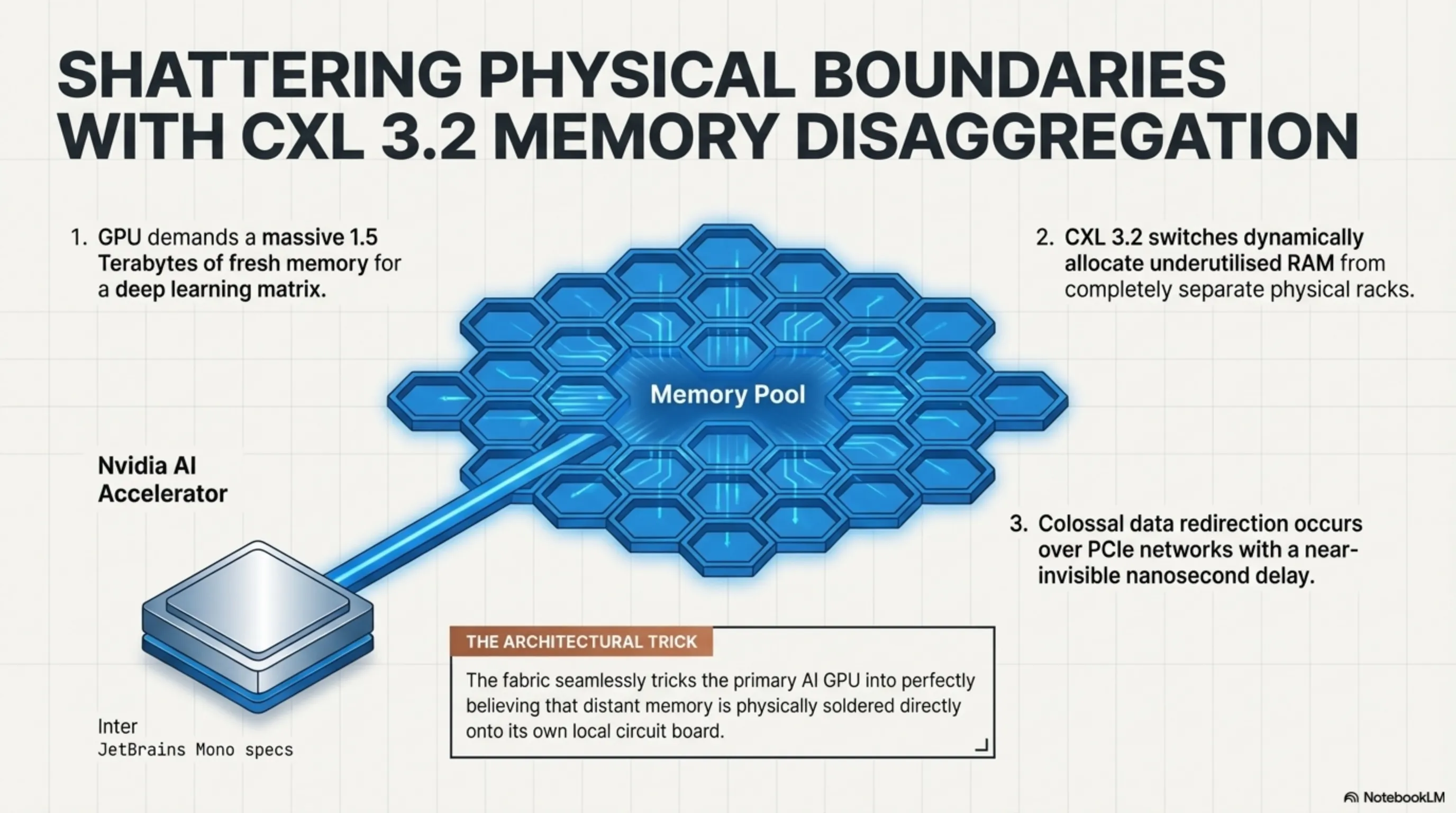

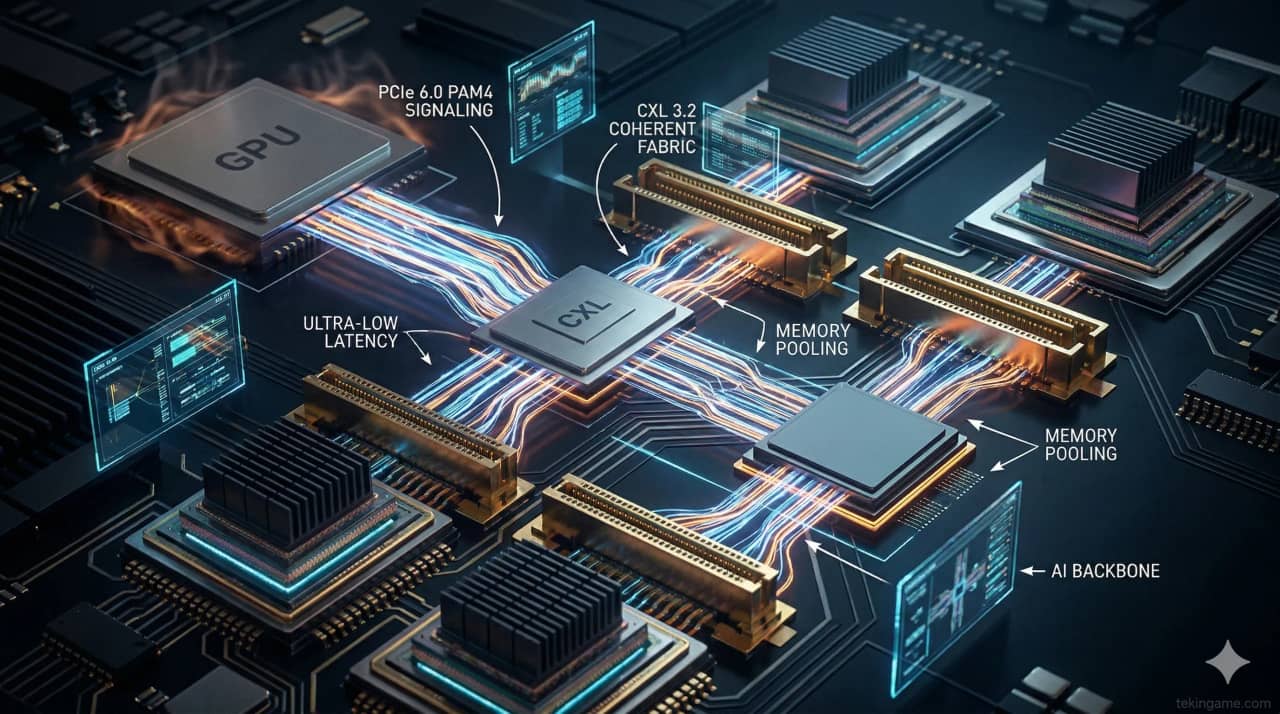

انقلاب بزرگ سال ۲۰۲۶ فقط محدود به سرعت نمیشود، بلکه مربوط به تغییر ذات معماری حافظه است از طریق تکنولوژی Compute Express Link (CXL). استاندارد CXL که بر روی بستر فیزیکی همان کابلها و اسلاتهای PCIe 6.0 حرکت میکند، آمده است تا مشکل «هدررفت عجیب حافظه» در دیتاسنترها را پایان دهد.

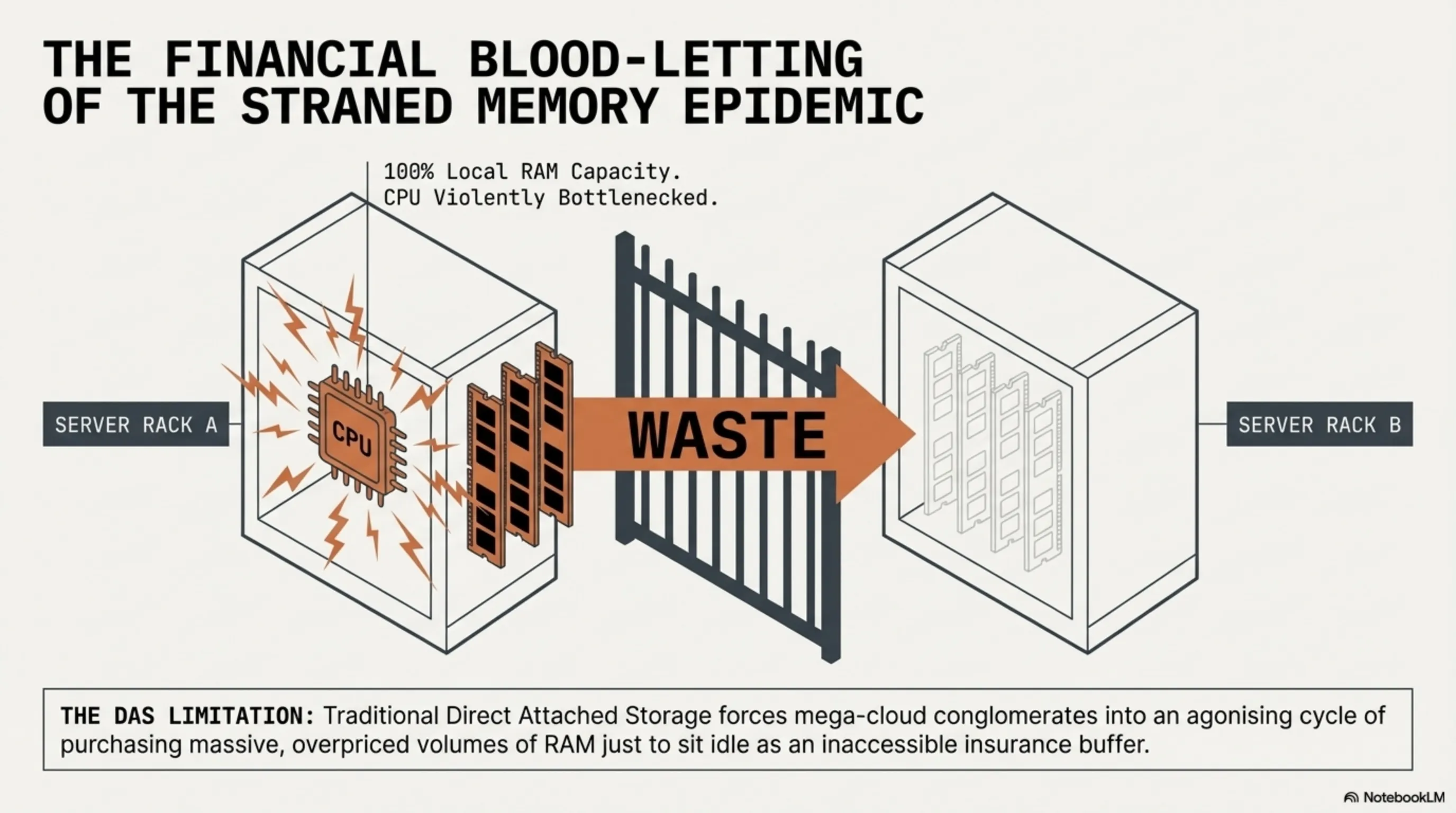

در سرورهای سنتی (Direct Attached)، هر پردازنده رم (RAM) اختصاصی خودش را دارد. اگر CPU شماره یک نیاز به رم بیشتری داشته باشد اما تمام ماژولهایش پر شده باشد، نمیتواند از رم خالیِ CPU شماره دو در یک رَک (Rack) دیگر استفاده کند؛ این پدیده "تکهتکه شدن حافظه" (Stranded Memory) نامیده میشود و سالانه میلیاردها دلار به شرکتهای ابری ضرر میزند زیرا آنها مجبورند مدام رم بلااستفاده بخرند.

اما با استاندارد CXL 3.2، مفهوم "تجزیهپذیری حافظه" (Memory Disaggregation) و "فابریک سوئیچینگ" عملی میشود. اکنون با استفاده از سوئیچهای CXL 3.2 در دیتاسنترهای بزرگ جهانی در سال ۲۰۲۶، تمام ظرفیت ماژولهای رمِ دهها سرور، به صورت یک استخر حافظه عظیم و پیوسته درآمده است. اگر پردازنده انویدیا در یک سرور ناگهان برای کامپایل کردن دیتای هوش مصنوعی به ۱ ترابایت حافظه بیشتر نیاز داشته باشد، CXL به صورت پویا (Dynamic) و با تاخیری در حد چند نانوثانیه، رم بلااستفادهی سرور همسایه را از طریق کابل ارتباطی در اختیار آن گرافیک قرار میدهد، گویی که آن رم به طور فیزیکی به پردازنده همان گرافیک متصل است! این یک انقلاب بیرحمانه علیه هزینههای سنگین سختافزاری است.

بخش پنجم: تراشههای Retimer شرکت Astera Labs و زیرساخت Microchip

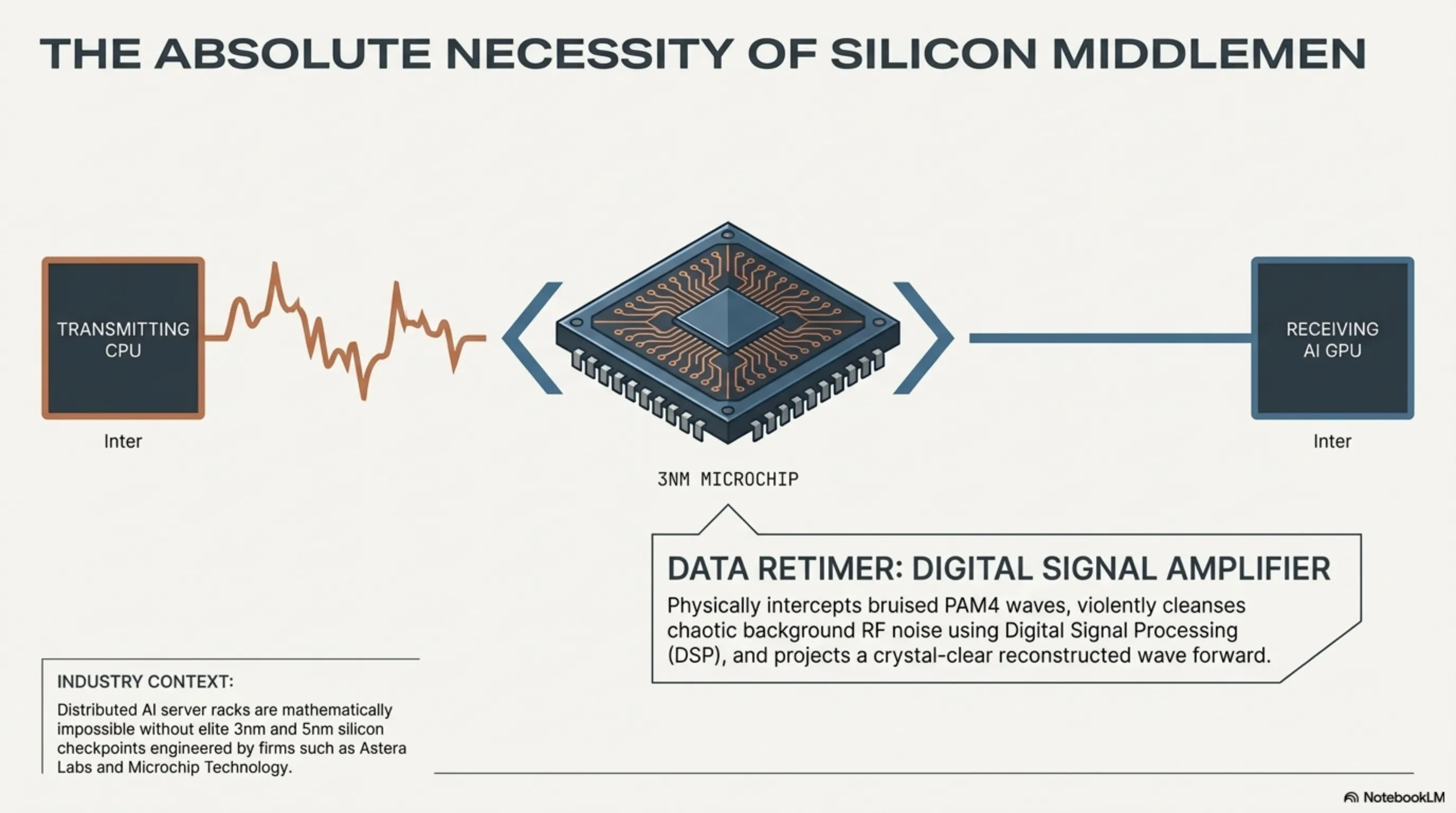

عبور دادن سیگنالهای ۶۴ گیگاترانسفری روی بردهای فیبری یا مسیرهای طولانی داخل سرور اصلا کار راحتی نیست و با افت شدید سیگنال مواجه هستیم. اینجاست که در سال ۲۰۲۶، شرکتهای تخصصی مانند Astera Labs و Microchip با فروش تراشههای فوقتخصصی به نام Retimer درآمدهای افسانهای کسب کردند.

یک Retimer در اصل یک "ایستگاه تقویت و بازسازی دیجیتالی سیگنال" است که در وسط مسیر ارتباطی کابل PCIe قرار میگیرد. این چیپست، سیگنال کاملاً مغشوش و تخریب شدهی PAM4 را در اواسط کابل دریافت کرده، تمام نویزهای آن را با تکنولوژی DSP شسته و پاکسازی میکند، و سپس سیگنال دیجیتالی بکر و کامسماً تمیزی را با همان قدرت اولیه بازسازی کرده و به سمت پردازنده هدف ارسال میکند. بدون حضور گسترده و استراتژیک این چیپستهای ۳ نانومتری و ۵ نانومتری از سوی Astera و Microchip، طراحی و مونتاژ هیچ سرور هوش مصنوعیِ مدرنی که قطعات آن با کابل از هم فاصله دارند، غیرممکن میبود.

بخش ششم: تاثیر فوری بر شتابدهندههای هوش مصنوعی (سری B200 انویدیا و MI400 ایامدی)

رونمایی از نسل کامپیوترهای سرپرست هوش مصنوعی (AI Supervisor Racks) در نیمه دوم ۲۰۲۶ توسط انویدیا، متکی بر درگاههای اتصال مستقیم PCIe 6.0 است. برای ساختن مدلی مانند GPT-5، شما نمیتوانید فقط از سوئیچهای اختصاصی مثل NVLink استفاده کنید؛ شما نیاز دارید کارتهای شبکه دهها هزار گیگابایتی و درایوها NVMe را به سرعت به GPU خوراک بدهید.

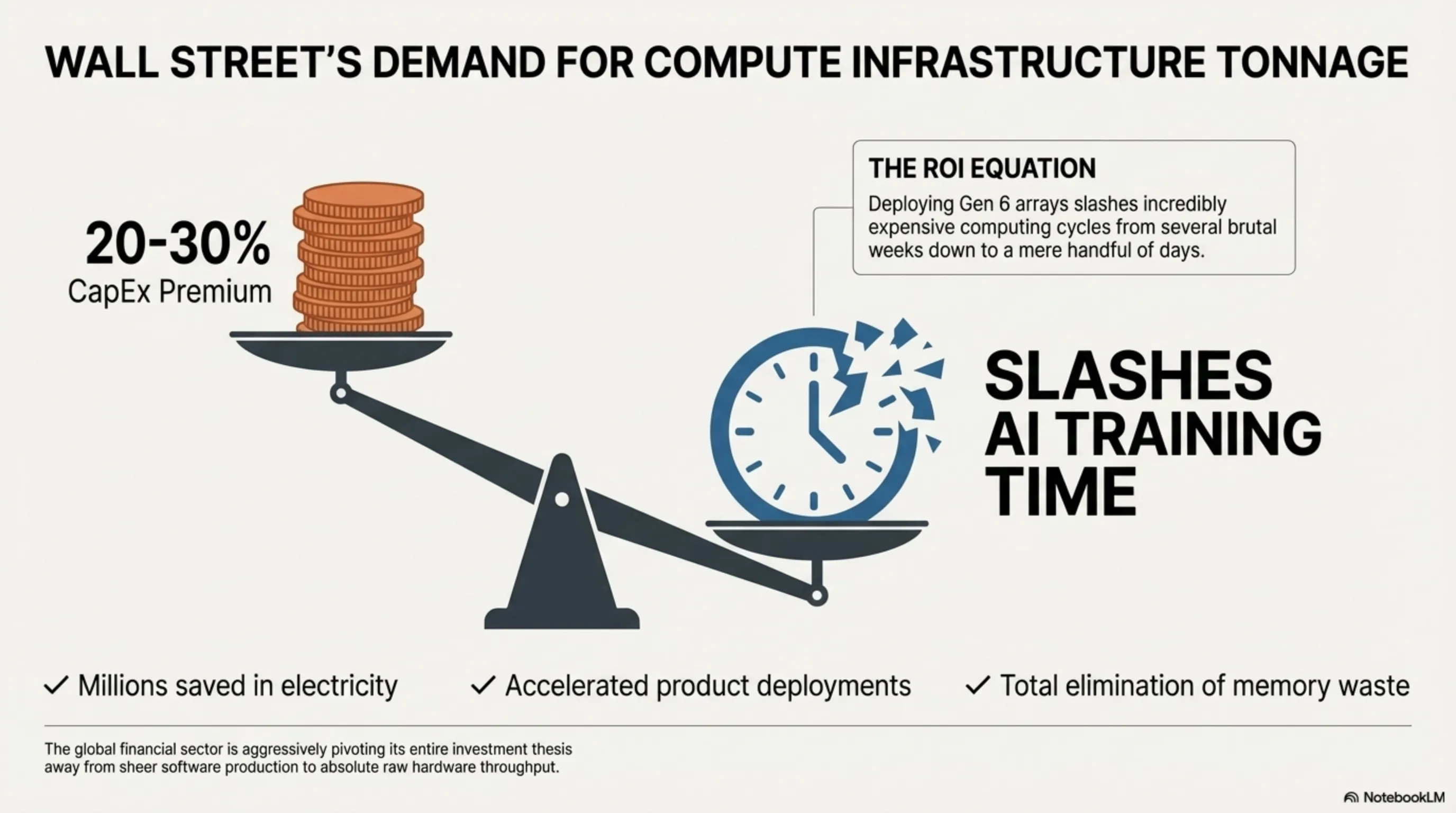

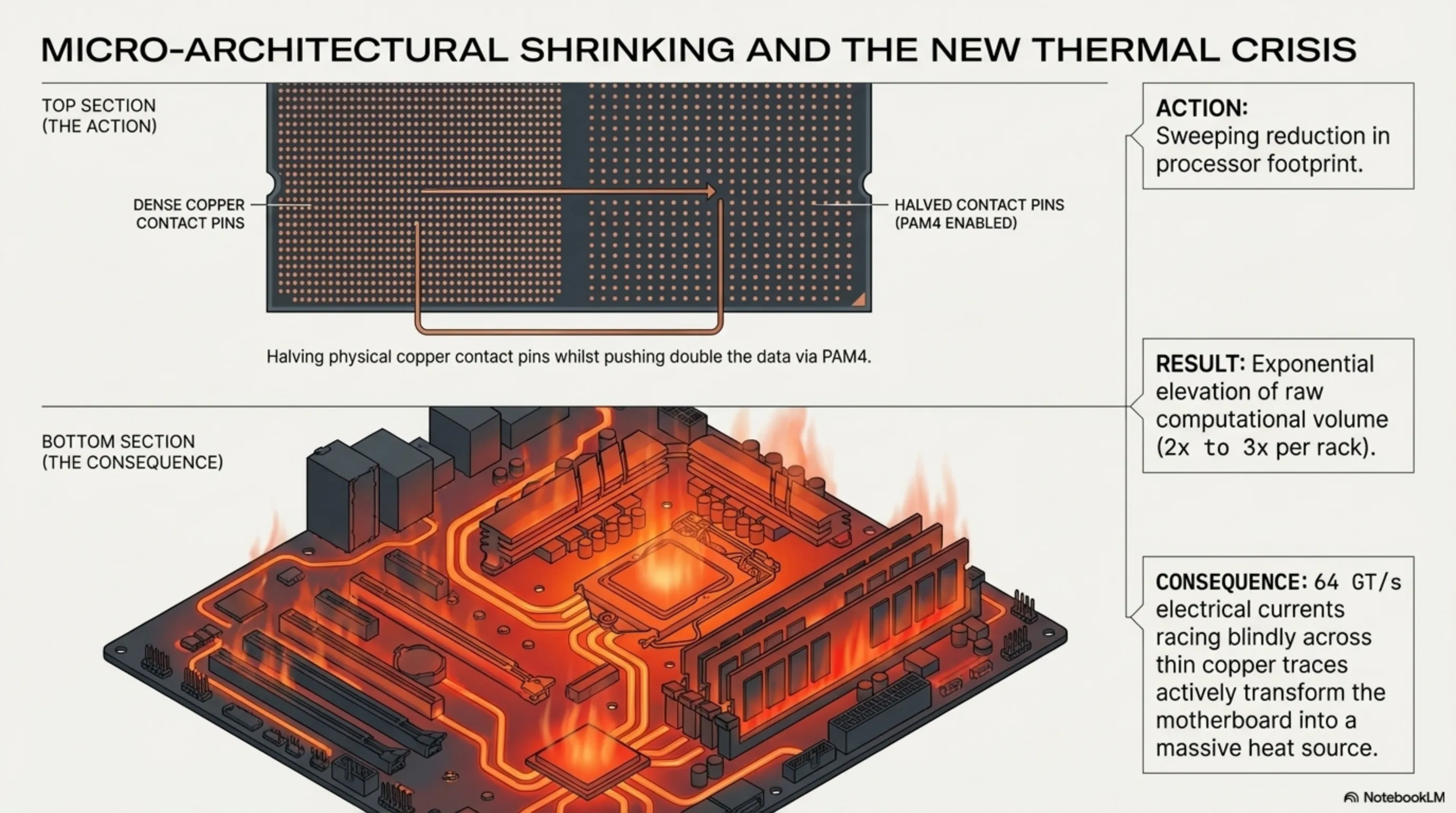

مهاجرت به PCIe Gen 6 این اجازه را به شرکتهای طراحی سیلیکون داد که به جای ساخت پینها و پایههای بزرگ برای انتقال دیتای زیاد، پایهها را نصف کنند و در عوض از همان پایههای کمتر، اما با سرعت دو برابرِ PAM4 استفاده کنند. این امر مستقیماً باعث کوچکتر شدن اندازه پردازنده روی برد و همچنین کاهش شدید حرارت محیطی در سرورهای ابری گردید و ظرفیت محاسباتی هر Rack در دیتاسنترهای مدرن را تا دو الی سه برابر افزایش داد.

بخش هفتم: مکانیک خنککننده: دفع حرارت در محیطهای پردازشی با فرکانس 64 GT/s

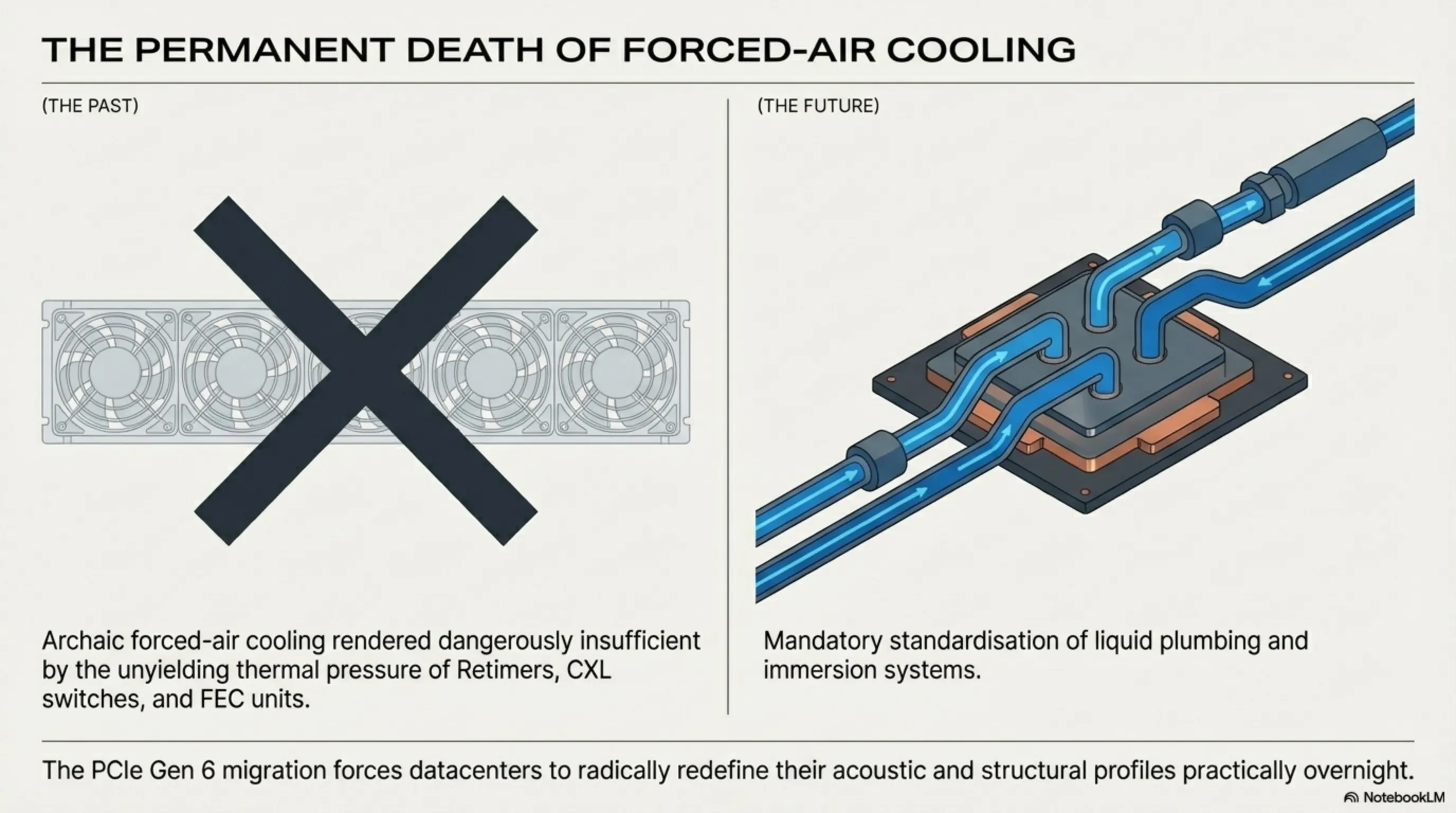

یکی از پیامدهای شدیداً نادیده گرفتهشده اما مرگبار از ادغام گذرگاههای PCIe 6.0 در سرورهای ابری، بحران مهندسی وحشتناک پیرامون دفع حرارت موضعی است. هرچند که خود پردازندهها موفق به کاهش ساختار سختافزاری خود شدهاند، جریانهای عظیم و خروشان الکتریکی با سرعت ۶۴ گیگاترانسفر بر ثانیه که کورکورانه روی مسهای نازکِ مادربرد در حال گردش هستند، خودِ این بُردهای فیزیکی را به یک رادیاتور حرارتی عظیم و به شدت داغ تبدیل میکنند. تلفیق متراکم چیپهای Retimer، سوئیچهای سنگین CXL 3.2 و واحدهای محاسبهگر FEC که همگی تحت بار پردازشی ۱۰۰ درصد کار میکنند، تابش حرارتی فوقالعاده وحشتناکی ایجاد مینمایند.

این فشار حرارتی بیامان، بهسرعت سیستمهای سنتی خنککننده مبتنی بر فن (Air Cooling) را کاملاً منسوخ و برای این محیطهای متراکم خطرناک ساخته است. به همین علت، استقرار غولآسای معماری PCIe Gen 6 دیتاسنترهای جهان را عملاً وادار کرده است تا استفاده از فنها را کلاً کنار بگذارند و یکشبه، خنککنندههای مایع مستقیم با اتصال به چیپ (Direct-to-Chip Liquid Cooling) و سیستمهای خنککننده غوطهوری (Immersion Cooling) را به استاندارد قطعی تبدیل کنند.

بخش هشتم: تحلیل اقتصادی، هزینههای سرسامآور کابلکشی نوری و افول مس

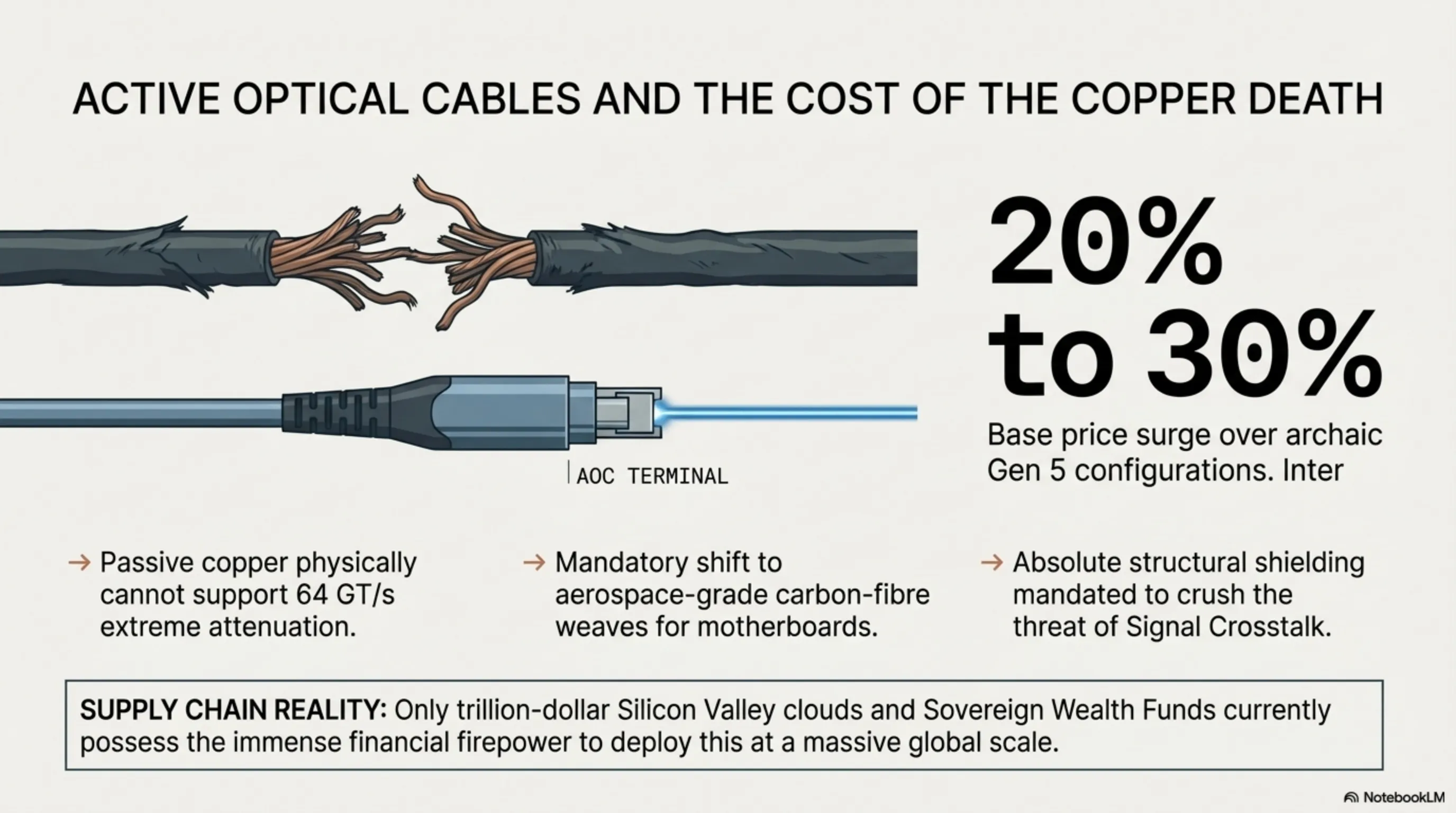

از نظر اقتصادی، تکنولوژی PCIe 6.0 یک چرخه پرهزینه است. کابلهای مسی معمولی به دلیل افت فرکانسی در طولهای بیش از چند ده سانتیمتر دیگر پاسخگو نبوده و تمام اتصالات طولانی باید توسط کابلهای اکتیو نوری (AOC) که قیمت بسیار نجومیتری دارند تعویض شوند. استفاده از مادربردهایی که فیبر کربن پیشرفته و ایزولاسیون کامل برای کاهش تداخل سیگنال (Crosstalk) دارند، قیمت سرور لخت (Bare metal) را ۲۰ تا ۳۰ درصد افزایش میدهد.

بخش نهم: وضعیت فعلی دیتاسنترها و سرورهای خاورمیانه در مواجهه با این جهش

با وجود پیشرفتهای خیرهکننده در سیلیکون ولی، وضعیت دیتاسنترها در خاورمیانه به دو دسته کاملاً متضاد تقسیم میشود. از یک سو، مراکزی مانند نئوم در عربستان سعودی و دیتاسنترهای دبی، با تزریق بودجههای دهها میلیارد دلاری در حال مهاجرت سریع به زیرساختهای مبتنی بر PCIe 6.0 و CXL 3.2 هستند تا جایگاه خود را به عنوان قطب جدید هوش مصنوعی تثبیت کنند.

برای شرکتهای فناوری منطقه خاورمیانه، عدم سرمایهگذاری روی این معماری جدید، به معنای پرداخت دائم هزینه برق گزاف برای سرورهای قدیمی، تحمل تلفات وحشتناک حافظه، و در نهایت خفگی کسبوکار و عقب ماندن از قطار توسعهی هوش مصنوعیِ سازمانی است.

بخش دهم: معماری امنیتی: یکپارچگی و رمزنگاری دادهها روی کابلهای رابط

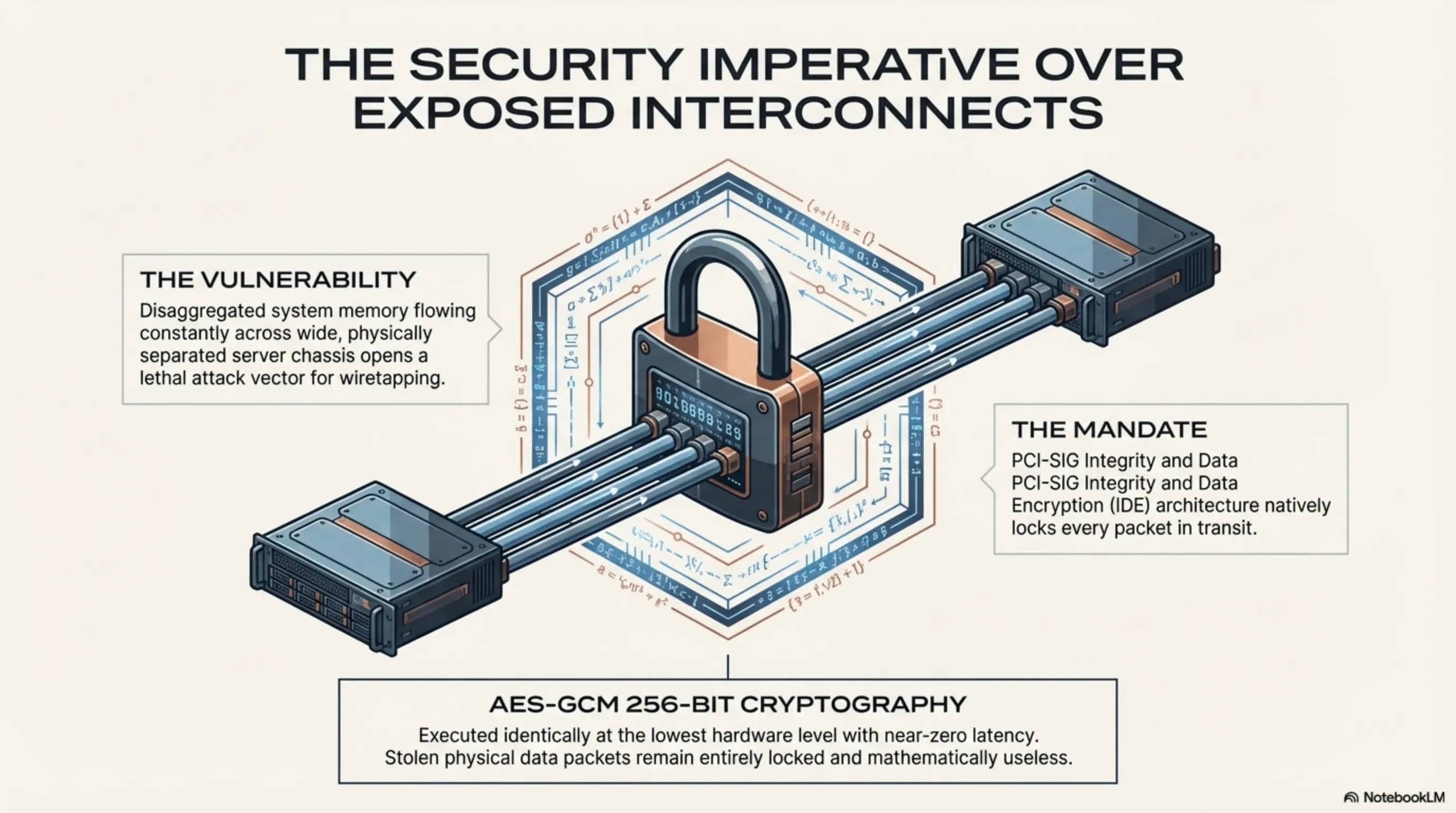

همزمان با شیفت دیتاسنترها به سوی معماری تجزیهپذیر (Disaggregated) که توسط پروتکل CXL 3.2 الزام شده است، یک بُردار حمله امنیتی عظیم نیز گشوده میشود. از آنجا که اطلاعات فوقحساسِ حافظههای رم (RAM) اکنون با سرعت بسیار بالا از طریق کابلهای فیزیکی بیحفاظ در حال تردد بین رَکهای سرورِ جداگانه میباشند، مفهوم قدیمی امنیت محلی کاملاً از میان رفته است.

برای مقابله با این تهدید سیستمی، استانداردِ امنیتی IDE بهطور مستقیم در لایههای بنیادین پروتکلهای PCIe 6.0 ادغام نمود. به لطف توابع رمزنگاری پیشرفته سختافزاری AES-GCM 256-bit، تضمین داده شده که تکتکِ بیتهای داده در مسیر انتقالِ بین رکها رمزگذاری (Encrypted) شوند. حتی در صورت شنود فیزیکی، دادهها کاملاً غیرقابل استفاده باقی خواهند ماند.

بخش یازدهم: نتیجهگیری - تنها راه نجات برای ترافیک پردازشی مگا-اسکیل

دهه سوم قرن بیست و یکم به ما ثابت کرد که پردازشگرها (CPU و GPU) دیگر به تنهایی نمیتوانند تمدن دیجیتال را به دوش بکشند. گلوگاه اصلی اکنون "انتقال دیتا" است. اگر بهترین پردازنده جهان نتواند دادهها را با سرعت کافی از اینترفیس شبکه یا رم بخواند، عملاً به یک بخاری گرانقیمت تبدیل میشود. مهاجرت به PCIe 6.0 و CXL 3.2 تنها یک آپگرید پرسرعت نیست، بلکه یک تغییر پارادایم اساسی در فیزیکِ کلاسترها است.

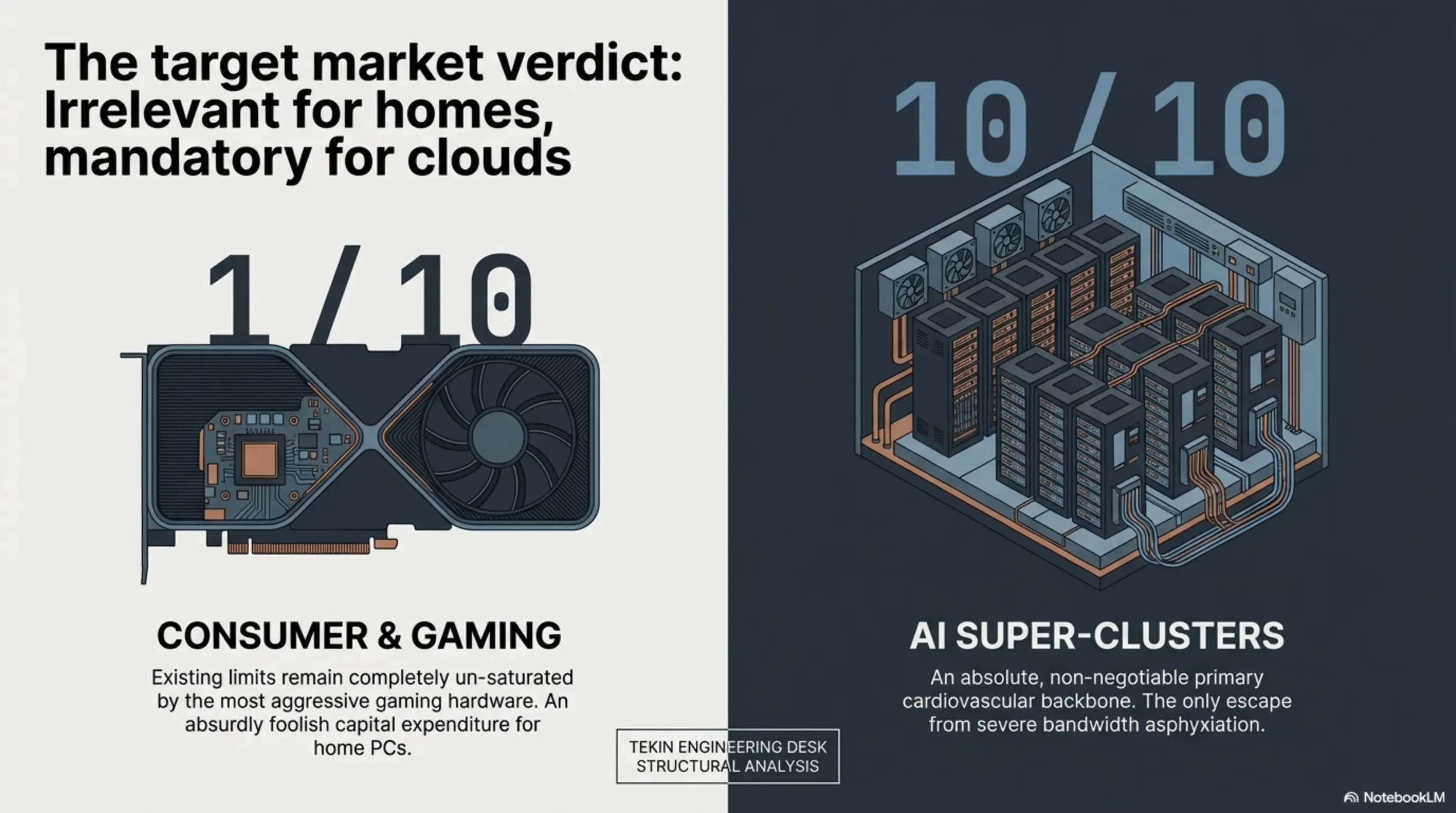

حکم نهایی تیم فیزیک سختافزار تکین گیم: تنها راه فرار از خفقان پهنای باند

ارزش خرید برای کامپیوترهای خانگی و گیمينگ سیستم (Gamers): ۱ از ۱۰ (گذرگاههای PCIe 4.0 و PCIe 5.0 هنوز هم به هیچ وجه توسط قدرتمندترین کارتهای گرافیک گیمینگ مانند RTX 5090 پر نشدهاند. این معماری فعلاً برای مصارف خانگی یک هزینه احمقانه است.)

نقش حیاتی در صنعت Cloud و AI Infrastructure: ۱۰ از ۱۰ (شاهرگ حیاتی و مطلق برای زنده ماندن تراشههای شتابدهنده نسل بعدی)

پایان کلام: معماری PCIe Gen 6.0 و مکمل بینظیر آن CXL 3.2، یک تکامل معمولی "نسخه به نسخه" نیستند. این در واقع اعتراف صنعت سیلیکون به رسیدن به انتهای تواناییهای مدولاسیون قدیمی در نسل پنجم بود. این تغییر زبان سیگنالینگ به PAM4، به علاوه استخرهای ابری برای تبادل پویای حافظه اثبات میکند که کامپیوترهای سرور در حال تبدیل شدن از یک "کیس حاوی چند قطعه مجاور هم" به یک "مغز متصل و پراکنده به هم در عرض دهها متر" هستند. بدون این فناوریهای نامرئی و چیپهای ریتایمر گرانقیمت، ساختن غولهای ابری هوش مصنوعی کاملاً محال میبود.

گالری معماری تخصصی دیتاسنتر