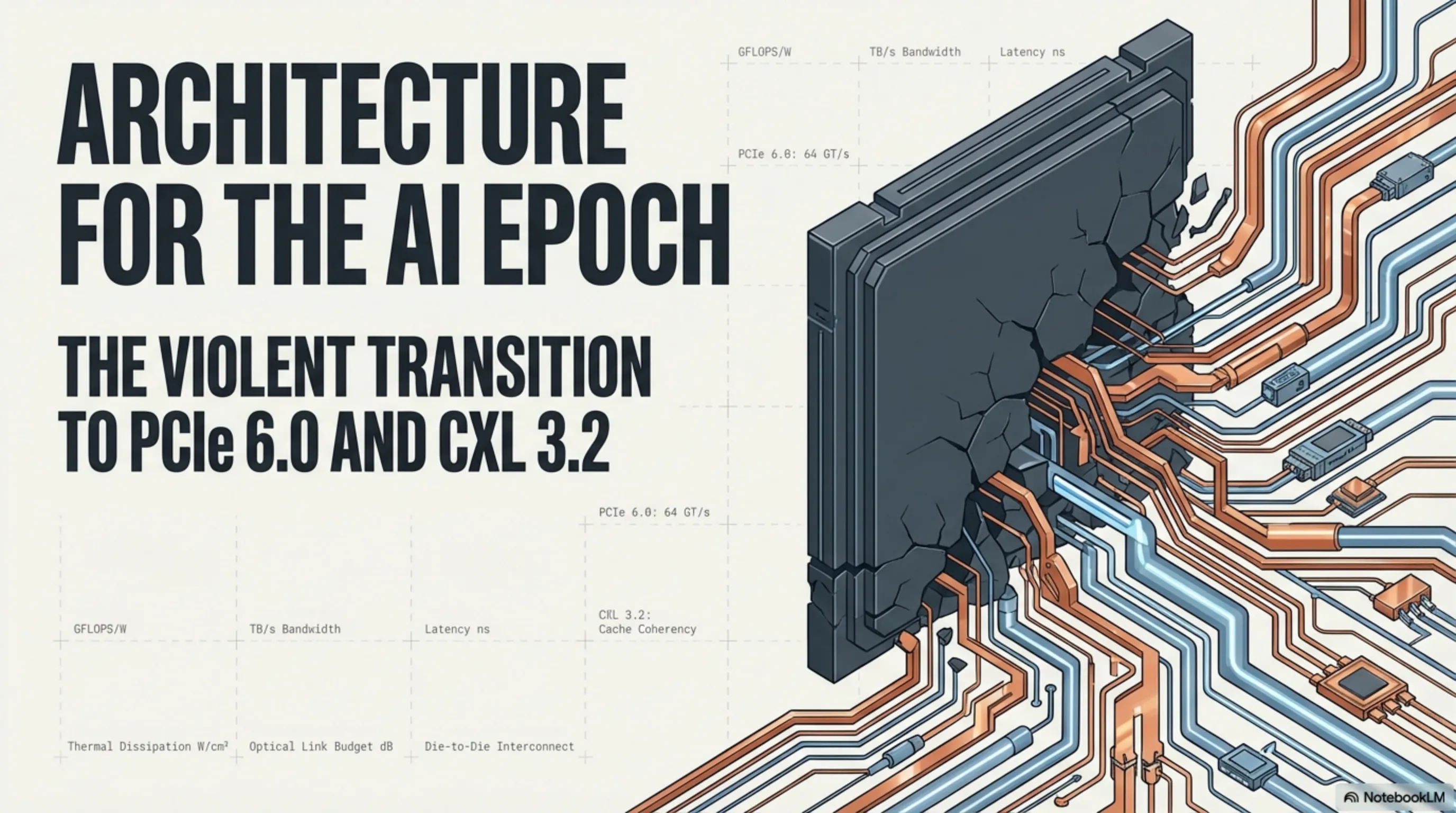

تحليل شامل في عام 2026 حول الهجرة الصناعية نحو معيار PCIe 6.0 وبروتوكول CXL 3.2 لمواجهة اختناقات البيانات في عصر الذكاء الاصطناعي. نستعرض تقنية PAM4 وتصحيح الأخطاء الأمامي (FEC) كمفاتيح لمضاعفة السرعة إلى 128 جيجابايت/ثانية. كما نناقش ثورة "تفكيك الذاكرة" وتأثير هذه التقنيات على مراكز البيانات في الشرق الأوسط، خاصة في نيوم ودبي، ودور شرائح Retimer في تأمين استقرار الشبكات.

القسم الأول: مقدمة والنهاية المفاجئة لحكم PCIe Gen 5

خلال السنوات التكوينية العميقة في أواخر عام 2024 وامتدادها المباشر إلى عام 2025، كان الكشف الكبير والنشر الضخم اللاحق لمعماريات المعالجات المؤسسية المستخدمة في الخوادم العالمية والمجهزة بشكل أساسي وجوهري بتوجيه مسار ناقل البيانات PCIe 5.0 يُعلن ويُحتفل به بشكل شبه عالمي باعتباره إنجازاً تاريخياً وجيلياً حاسماً ومحدداً في عالم الأجهزة والخوادم الفائقة. كانت المضاعفة الفيزيائية المطلقة لعرض النطاق الترددي الخام للربط البيني مقارنة بقيود الجيل الرابع PCIe 4.0 المتقادمة والبائسة تبدو منطقياً ورياضياً كافية وسخية بشكل مريح لإشباع وتلبية متطلبات نقل البيانات النهمة والجشعة بشكل غير قابل للإشباع للخوادم الفائقة الحديثة لما تبقى من العقد الحالي على الأقل وربما أبعد من ذلك بكثير في المستقبل المنظور.

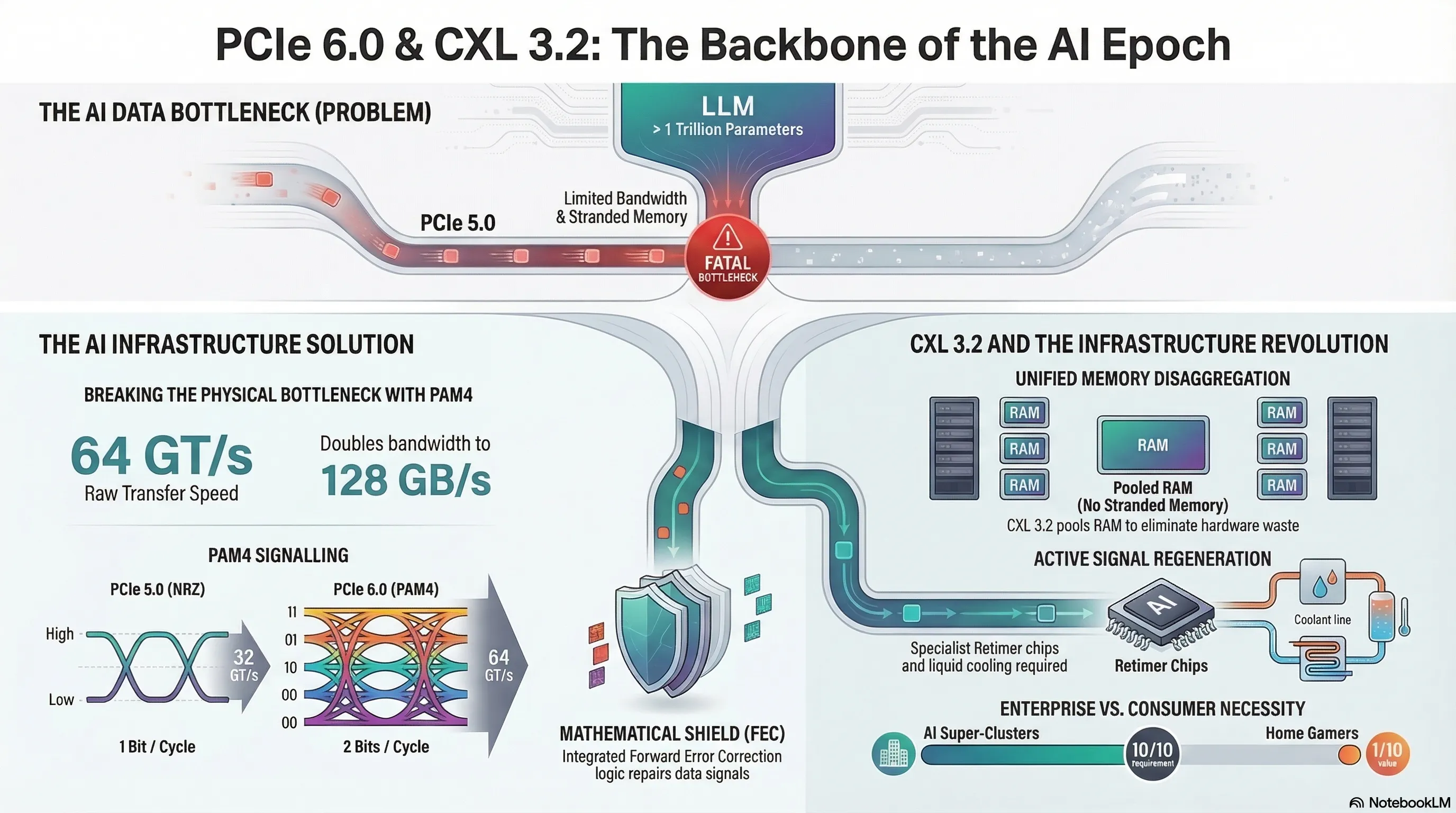

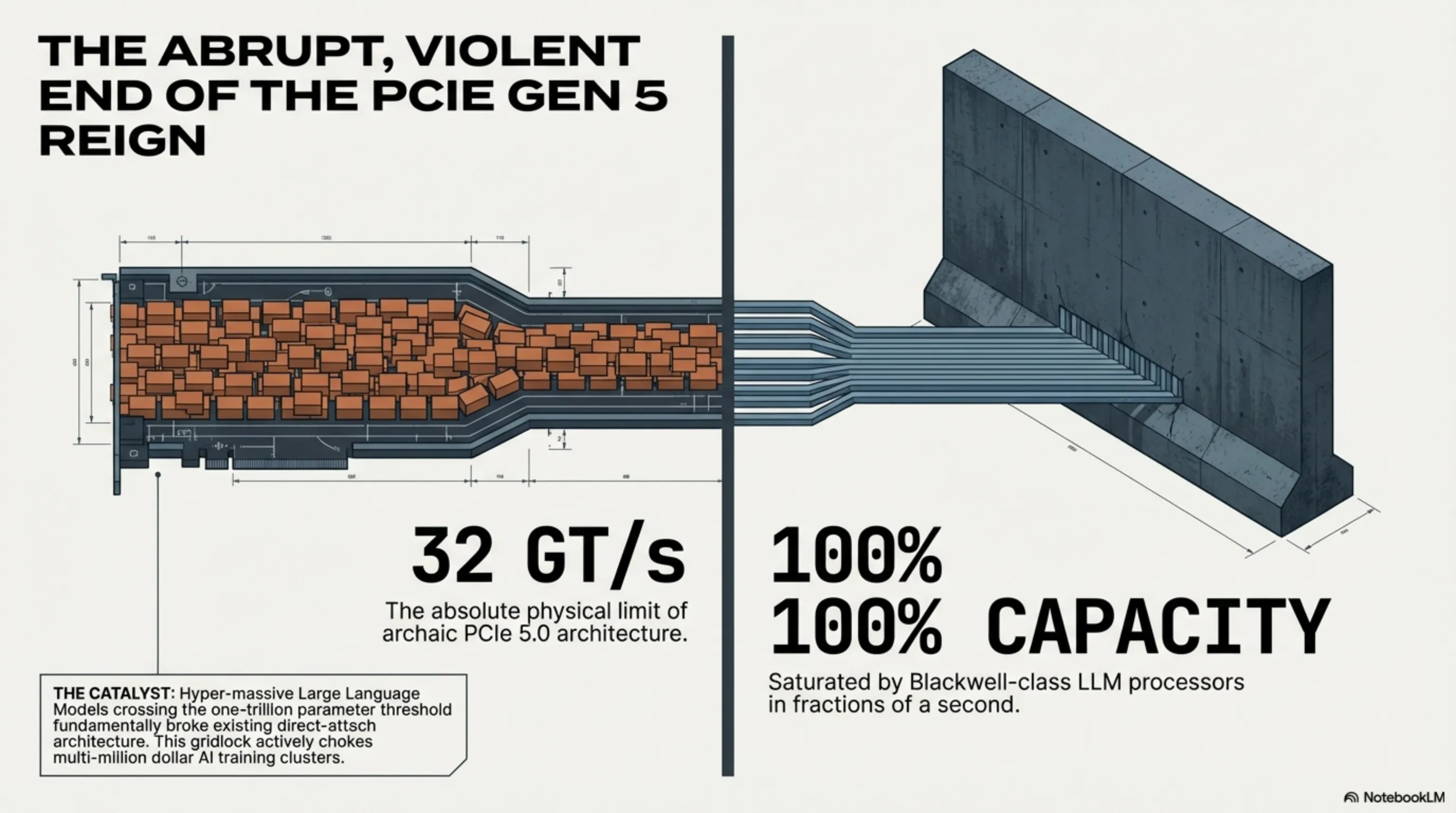

ومع ذلك ولكن وبشكل مأساوي ودراماتيكي ومتوحش، فقد أدى الانفجار غير المسبوق والعنيف بشكل صادم ومفاجئ في التدريب التجاري الضخم لنماذج اللغات الكبيرة جداً (LLMs) - والتي تتجاوز في كثير من الأحيان وبتكرار مفزع عتبة التريليون معامل (Trillion-Parameter) المذهلة - بالإضافة إلى الضرورة القسرية المطلقة والحتمية اللاحقة للمعالجة الرسومية فائقة الثقل والاستمرار المتواصل باستخدام المعالجات الرسومية (GPU) طوال عام 2025 ومباشرة في عام 2026، أدت مجتمعة بمهندسي السيليكون النخبة والمتمركزين بعمق داخل عمالقة التكنولوجيا مثل Nvidia و AMD و Broadcom إلى الاصطدام العنيف وجها لوجه بحقيقة هندسية مرعبة ومتأصلة لا تقبل التغيير ولا المساومة: أصبح واضحاً فورياً ورياضياً ولا يقبل الجدل أن حتى امتلاك سرعة ناقل تبلغ 32 غيغا ترانسفير في الثانية (GT/s) كانت في طريقها سريعاً ومرعباً للتحول إلى عنق زجاجة (Bottleneck) كارثي وقاتل تماماً يخنق الحياة بنشاط وشراسة من مجموعات تدريب الذكاء الاصطناعي التي تكلف ملايين الدولارات.

إن وحدات المعالجة الرسومية القوية بشكل هائل ومخيف والحديثة والرائدة - وأبرزها بشكل ملحوظ سلالة Blackwell الوحشية من Nvidia (معمارية ناقشنا ديناميكيات تصديرها المقيدة بشدة والتي زعزعت استقرار قطاعات تقنية آسيوية محددة مؤخراً) - تلتهم وتستنفد بيانات المصفوفات التنسورية المحلية بوتيرة كانت تُعتبر سابقاً مستحيلة فيزيائياً بالمطلق. فهذه المعالجات المتخصصة والنخبوية في مجال الذكاء الاصطناعي قوية بشكل لا يقبل التصديق لدرجة أنها أثناء مراحل التحميل والتنفيذ المكثفة والمستمرة لنماذج الأساس ذات المليارات من المعاملات والوزنات الكثيفة، تمتلك القدرة الفعلية والمطلقة على إشباع كامل ممرات PCIe 5.0 المتاحة في اللوحة الأم للخادم بالكامل، غارقة في حالة ازدحام بنسبة 100% في جزء بسيط من ثانية واحدة مجردة. لذلك وفي ربيع عام 2026 الحاسم والمحوري، كان الرد الرسمي والمحلي الممنهج الذي شنته صناعة الخوادم المؤسسية العالمية لمكافحة هذه الأزمة الفيزيائية الحادة بقوة، هو الهجرة التشغيلية المنسقة والضخمة تماماً نحو معيار PCIe Gen 6.0 المتقدم جذرياً.

القسم الثاني: هندسة إشارات PAM4 في PCIe Gen 6.0

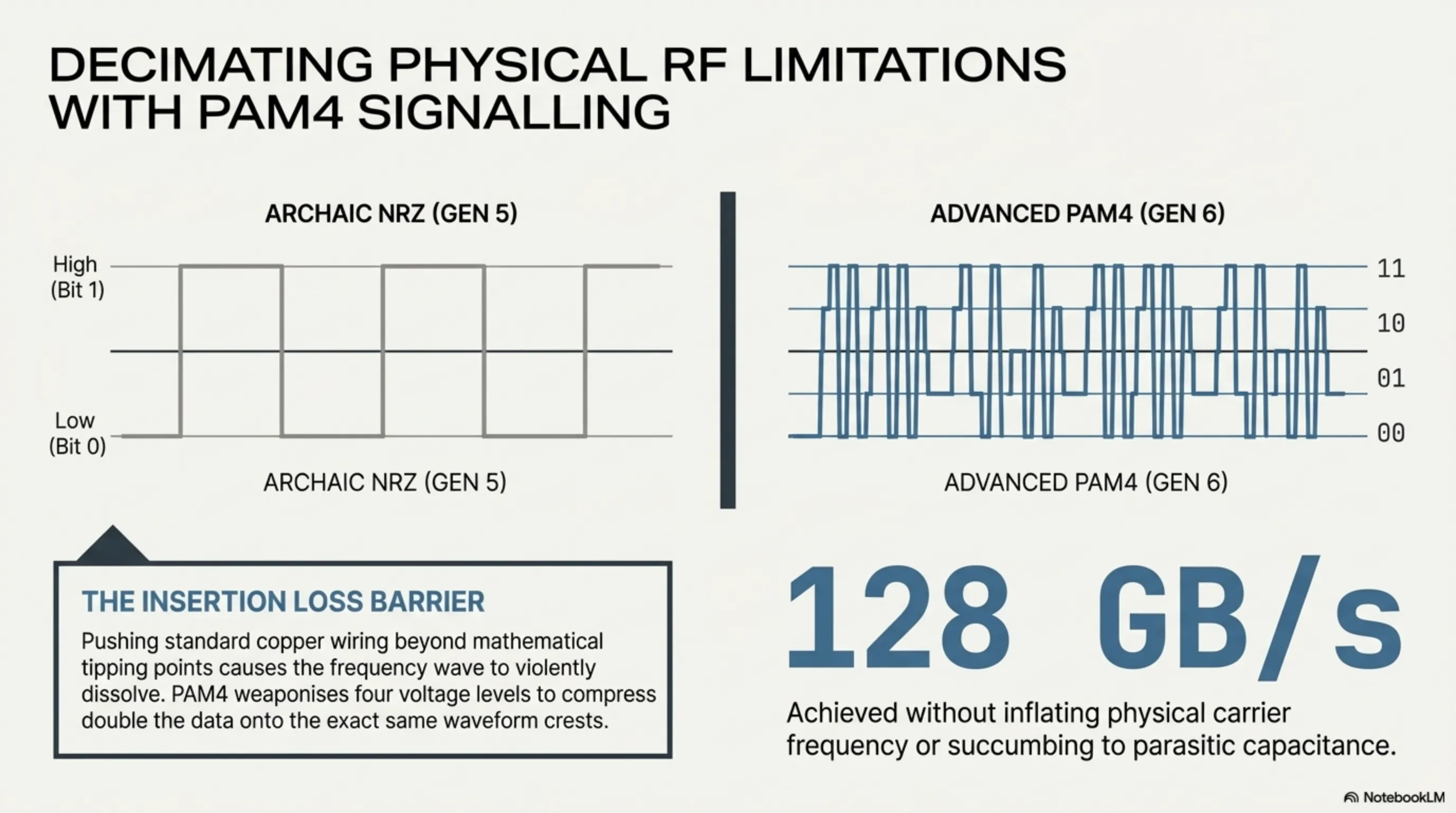

منذ التأسيس المطلق والجذري لأول نسخة من معيار PCIe قبل أكثر من عقدين من الزمن، واستمراراً دون انقطاع حتى نشر مواصفات الجيل الخامس (Gen 5)، اعتمدت كل نسخة بشكل موالي ومخلص ودون تساؤل على منهجية ترميز إشارة رقمية كلاسيكية ومتميزة ومحددة للغاية تُعرف صارمة باسم NRZ أي (Non-Return-to-Zero). وبشكل جوهري وأساسي ضمن البنية الصارمة لـ NRZ، يتعرف النظام ويعتمد فقط حصرياً على مستويين اثنين فقط من الجهد الكهربائي المتباينين بشكل جذري عن بعضهما: نبضة جهد عالي (والتي يفسرها المعالج بنشاط ويحسبها كبت ثنائي 1)، ونبضة جهد منخفض (تُحسب رياضياً كبت ثنائي 0).

كان الجدار الهندسي القاسي والمستعصي الذي يعيق هذه المنهجية المعينة هو أن القوانين الأساسية والراسخة لفيزياء الكم والكهرومغناطيسية ترفض بشكل قاطع بلا استئناف ولا رجعة السماح للمهندسين ببساطة بتسريع وتضخيم التردد الحامل الفيزيائي الأساسي (Carrier Frequency) عبر الأسلاك النحاسية القياسية وآثار لوحة الدوائر المطبوعة الهشة إلى مستويات لا نهائية. إن توسيع وزيادة تردد الجهد الكهربائي المادي بشكل عدواني ومفرط إلى ما بعد نقاط الانقلاب الرياضية الصارمة يتسبب حتماً في إطلاق الظاهرة المدمرة للغاية المعروفة تقنياً باسم "خسارة الإدراج" (Insertion Loss) ويسبب "تدهور الإشارة" الهائل، حيث تتدمر موجة التردد نفسها بعنف وتذوب أثناء سفرها عبر الطول المادي للكابل أو عبر اللوحة الأم.

للالتفاف بقسوة وإبادة هذا القيد المادي الشديد بشكل فعال دون التخلي عن النحاس كلياً، نفذ المهندسون العباقرة النخبة الذين يشكلون اتحاد PCI-SIG العالمي محوراً معمارياً عنيفاً بشكل ملحوظ أثناء الصياغة الأساسية لخط أساس PCIe 6.0. اتخذوا القرار النهائي والحاسم والذي لا رجعة فيه بالتخلص الكامل والقطعي من منهجية NRZ العتيقة البالية ورميها مباشرة في مزبلة تاريخ الحوسبة والتكنولوجيا الرقمية، وبدلاً من ذلك ألزموا وفرضوا بنية تعديل سعة النبض رباعي المستويات (PAM4 - Pulse Amplitude Modulation 4-level) المتقدمة بشكل جامح ليتم تنفيذها بشراسة عبر جميع حارات الاتصال الأساسية للخوادم والبنية الحوسبية المتقدم الحديثة.

بدلاً من استخدام مستويي جهد أساسيين فقط كما في السابق، تستخدم طوبولوجيا PAM4 المتطورة والمسلحة بنشاط أربعة مستويات جهد مادية متميزة تماماً ومنفصلة بدقة (يتم تفسيرها تسلسلياً كـ 00، 01، 10، 11). هذا التعديل المادي العميق للغاية يعني بشكل قاطع أنه خلال كل تقلب فردي واحد لموجة الإشارة الداخلية (كل دورة ساعة فردية)، يقوم الجهاز في نفس الوقت وبشكل متزامن بنقل بتين مستقلين تماماً من البيانات لكل حارة، ليحل مباشرة محل القيد السابق المتمثل في بت واحد فقط. النتيجة المعجزية هي أن PCIe 6.0 ضاعف عرض النطاق الترددي التشغيلي الخام إلى 128 غيغابايت في الثانية المذهلة تماماً (في فتحة x16 ثنائية الاتجاه) دون إجبار التردد الفيزيائي الأساسي على أن يصبح أكثر فوضوية!

القسم الثالث: تصحيح الأخطاء الأمامي (FEC): الدرع الرياضي ضد موت الإشارة

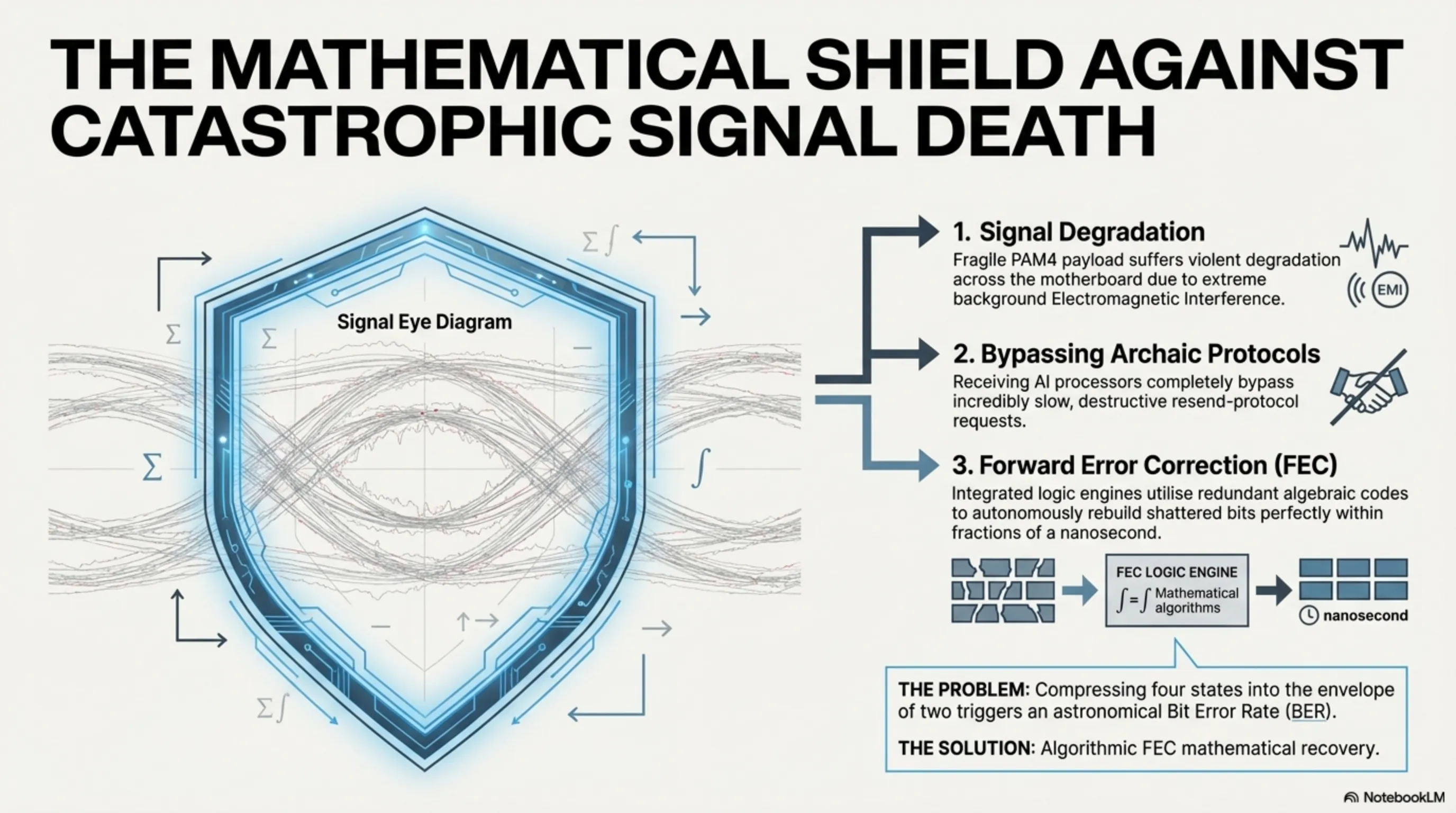

ومع ذلك ففي عالم هندسة السيليكون القاسي والمتطلب بلا هوادة، لا تُمنح أي قفزة ضخمة إلى الأمام مجاناً دون استخلاص ثمن باهظ ومؤلم لاحق. عندما تقرر بنية ما بجرأة حشر أربع حالات جهد محددة ودقيقة ومتباينة في نفس الغلاف الكهربائي المادي المجهري الدقيق الذي كان يستضيف سابقاً حالتين اثنتين فقط لا غير، فإن "مسافة الجهد" المميزة والموجودة بشكل طبيعي بين هذه المستويات المحددة الجديدة تنضغط وتتقلص بشكل جذري وخطير (وهو عرض يُعرف رسمياً بالانكماش الحاد لمخطط عين الإشارة - Signal Eye Diagram).

هذه الحالة المضغوطة بشدة والمعبأة بكثافة تجبر بطبيعتها الإشارات المرسلة على أن تصبح بشكل عميق وجامح قابلة للتأثر وهشة للغاية فيما يتعلق بأي تداخل كهرومغناطيسي محيط (EMI) أو ضوضاء خلفية عشوائية. وبالتالي فإن معدل خطأ البت الأساسي (BER) المتأصل أصلاً في إرسال PAM4 يرتفع بشكل فلكي مقارنة بالأنظمة القديمة. لمنع الانهيار الكلي والكارثي لنظام الشبكات بالكامل، فرضت مواصفات PCIe 6.0 رسمياً وبشراسة الدمج المنطقي العميق لوحدة استرداد رياضية مخصصة تُسمى رسمياً "تصحيح الأخطاء الأمامي" (Forward Error Correction - FEC). ضمن هذا النموذج، يقوم مُرسل البيانات الأصلي بنشاط بتجميع وحقن أكواد استرداد جبرية معقدة للغاية ومنطق استرداد احتياطي مباشرة بجانب حمولات البيانات الأساسية.

وبالتالي، عندما تعاني الحمولة حتماً من تدهور عنيف أثناء العبور المادي عبر اللوحة الأم ويتم تدمير عدة بتات رقمية فردية بشكل لا رجعة فيه بسبب التلوث الضوضائي، فإن المعالج الرسومي المستقبل - بدلاً من تشغيل بروتوكول "إعادة الإرسال" البطيء بشكل لا يصدق والمكلف للغاية والمدمر بشدة - يقوم بشكل مستقل تماماً وذاتياً بتشغيل محركات FEC المنطقية الرياضية المدمجة فيه. يستخدم الصيغ الخوارزمية المرفقة ليخمن ويعيد بناء ويصلح البت التالف بدقة متناهية خلال أجزاء من النانوثانية الواحدة. إن الزواج الحتمي والقسري بين بنية تردد PAM4 الكثيفة ومحرك التصحيح الرياضي FEC الذكي يعمل بشكل لا لبس فيه كالأساس المطلق والنهائي والحاسم الذي يحافظ على حياة واستقرار شبكات مراكز البيانات الثقيلة بشكل عنيف طوال عام 2026 وما بعده بكثير.

القسم الرابع: ثورة CXL 3.2: تفكيك الذاكرة (Memory Disaggregation)

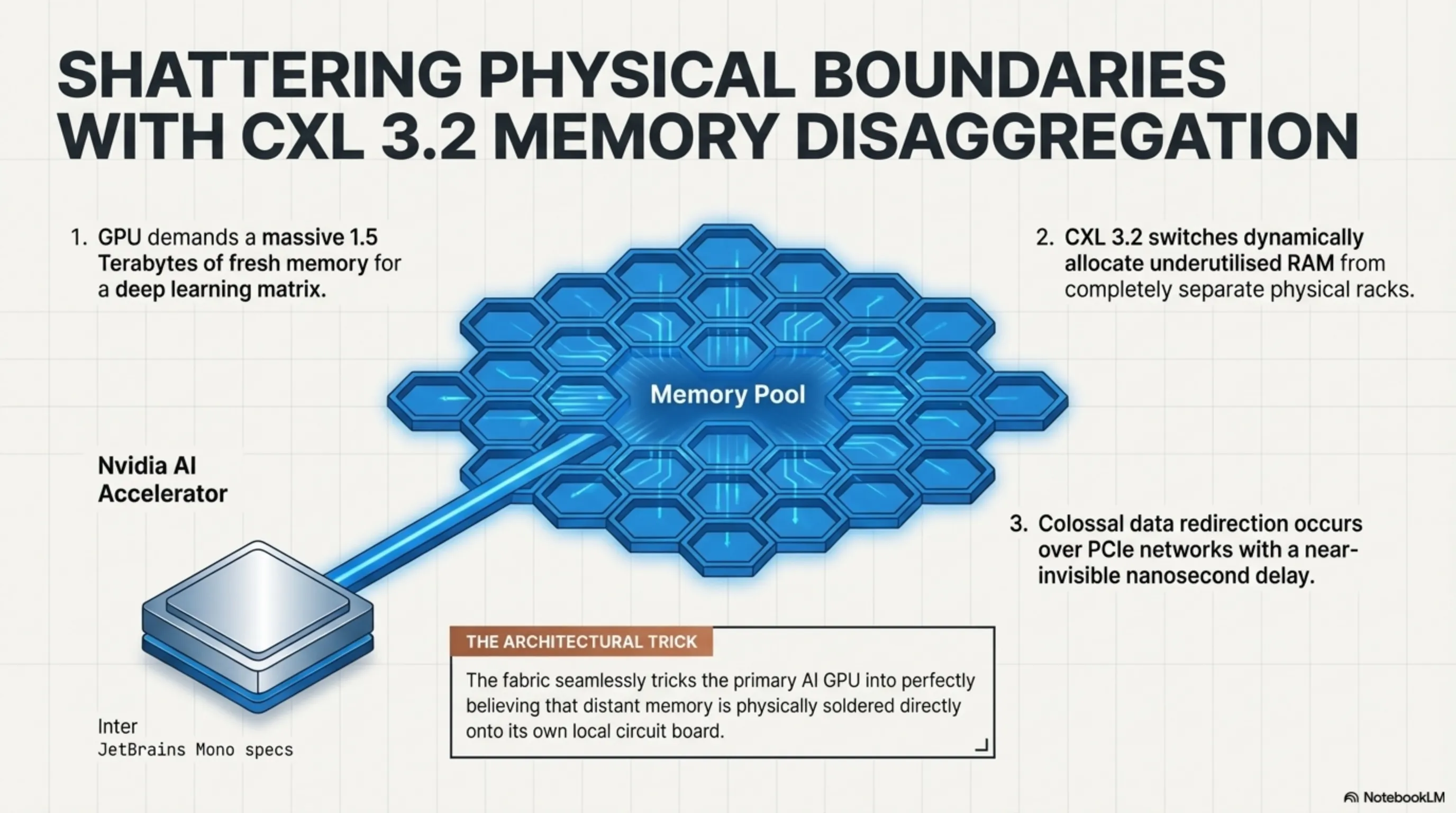

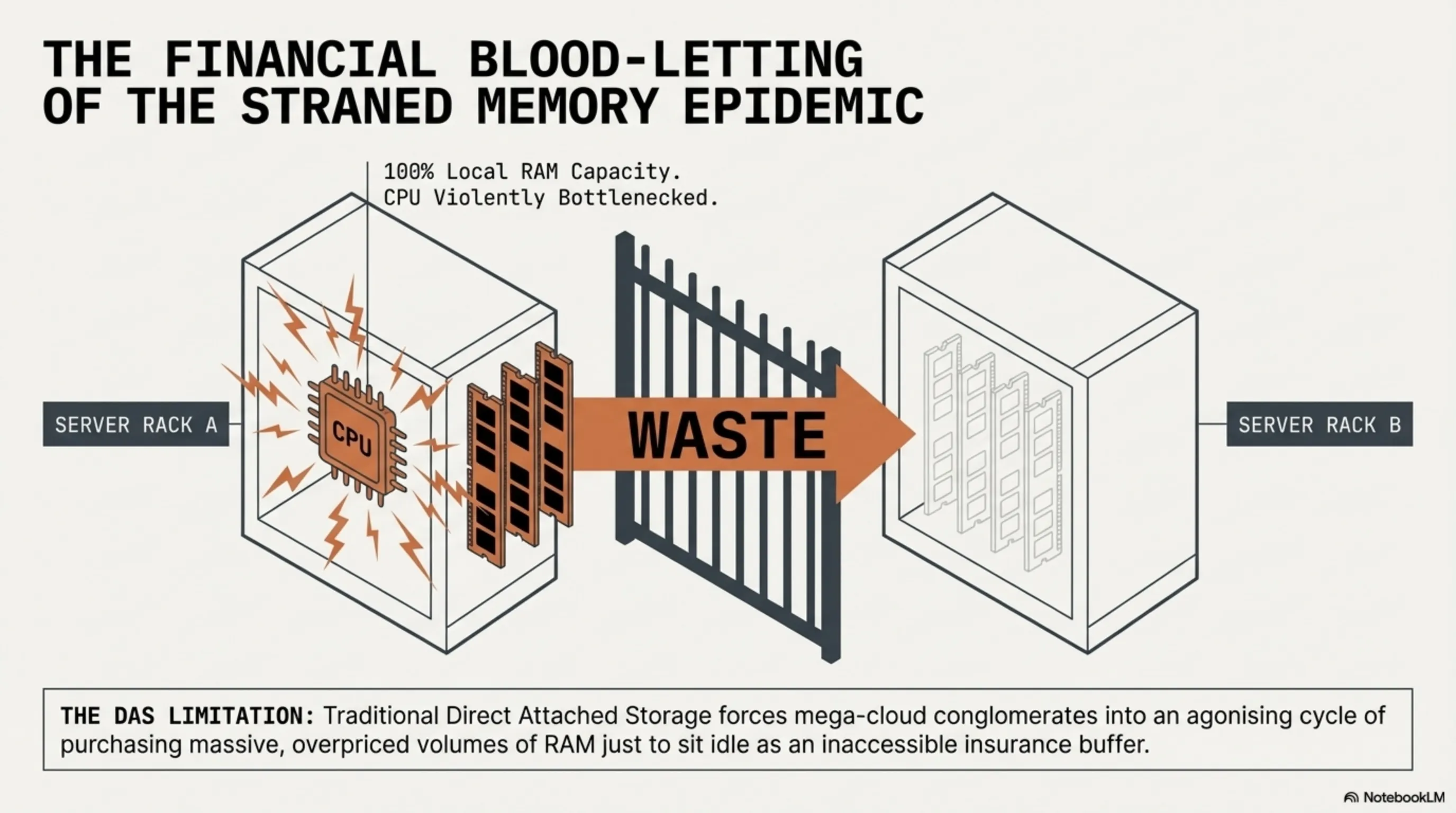

إن الثورة الهائلة في مراكز البيانات التي تتجلى بنشاط طوال عام 2026 ترفض بشكل قاطع أن تكون مقيدة فقط بالزيادات الوحشية في سرعة النقل المطلقة؛ فتأثيرها الأعمق والأكثر جوهرية يكمن بعمق في التفكيك المادي الكلي وإعادة الهندسة الجذرية لذاكرة النظام نفسها، مدفوعة بقوة لا تقاوم من خلال النضج الكامل والشامل لمعيار Compute Express Link (CXL). بروتوكول CXL يعمل أصلاً ومباشرة فوق نفس الآثار النحاسية الدقيقة والبنية التحتية العميقة لفتحات PCIe 6.0، لكن مهمته النهائية هي القضاء النهائي والحاسم على وباء "الذاكرة المعطلة" (Stranded Memory Epidemic) الكارثي مالياً الذي يعاني منه العالم.

في بيئات الخوادم التقليدية المبنية بشكل كلاسيكي (Direct Attached Storage)، يحتفظ كل معالج مركزي (CPU) فردي بمصفوفته الخاصة من ذاكرة الوصول العشوائي (RAM) المسيجة بصرامة والحصرية بالكامل. وبالتالي إذا احتاج المعالج رقم واحد فجأة إلى حقنة ضخمة وعدوانية من الذاكرة المؤقتة الإضافية لتجميع خوارزمية توسعية وكثيفة، ولكن فتحات DIMM المادية المحلية مشبعة بالكامل بنسبة 100%، فإنه لا يستطيع مطلقاً اقتراض أو الوصول إلى الذاكرة الشاغرة وغير المستخدمة تماماً الموجودة على المعالج رقم اثنين الموجود في حامل خوادم آخر. هذا القيد المادي القديم يجبر التكتلات السحابية الضخمة بمليارات الدولارات على دورة مؤلمة ومتوحشة من الشراء المستمر لأحجام هائلة مبالغ فيها من الذاكرة باهظة الثمن لمجرد أن تجلس خاملة كـ "احتياطي تأميني" مهدر تماماً.

مع النشر المؤسسي العدواني لمواصفات CXL 3.2 المتطورة بالكامل والتي تحقق مفهوم "تفكيك الذاكرة" (Memory Disaggregation) وشقيقه "التبديل النسيجي العميق" (Deep Fabric Switching)، تتحطم هذه القيود بشكل كامل وتام ولا رجعة فيه. الآن باستخدام محولات CXL 3.2 فائقة الكثافة الموجودة في قلب مراكز البيانات العالمية النخبوية لعام 2026، يتم إذابة سعات الذاكرة المحلية والمعزولة الممتدة عبر عشرات الحوامل والخوادم المادية المنفصلة تماماً وتوحيدها بشكل سحري في "مجمع ذاكرة" واحد ضخم ومتصل بلا حدود. إذا طالب مسرع Nvidia للذكاء الاصطناعي في الحامل A فجأة بحقن فوري لـ 1.5 تيرابايت من الذاكرة الجديدة، يقوم متحكم CXL الموحد بنشاط وديناميكياً وبسلاسة بتخصيص الحجم اللازم مباشرة من شرائح الذاكرة غير المستغلة فعلياً الموجودة في الحامل D، بتأخير لا يُرى يقاس بالنانوثانية فقط!

القسم الخامس: وسطاء السيليكون: Astera Labs و Microchip واحتكار شريحة Retimer

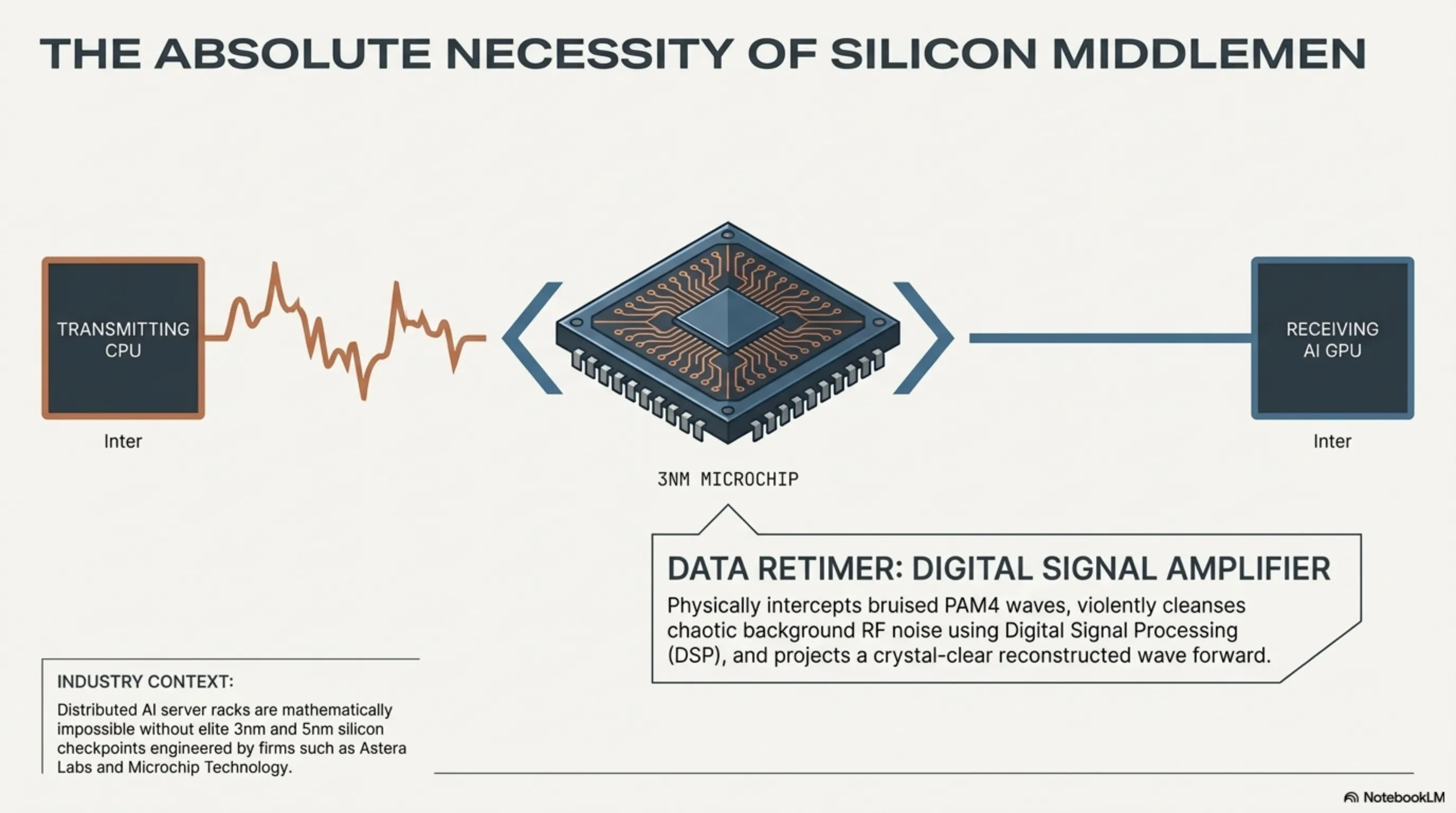

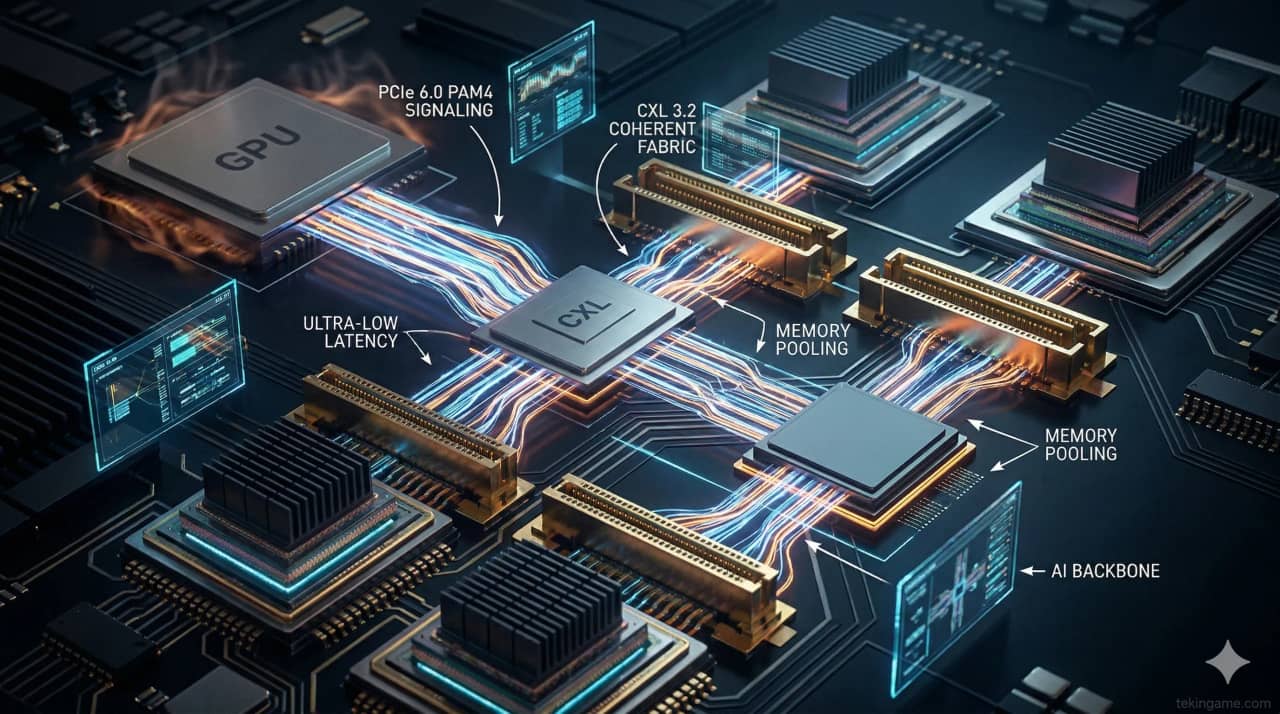

إن الإطلاق الناجح والمستمر لإشارة بتردد 64 غيغاترانسفير في الثانية (GT/s) بشكل مكثف عبر الألواح الليفية المزدحمة أو توجيهها عبر كابلات نحاسية طويلة تلتف داخلياً في هياكل الخوادم الضخمة ليس مهمة فيزيائية سهلة على الإطلاق؛ إنها عملية رياضية شاقة وتواجه حتماً درجات مدمرة من التدهور الحاد للإشارة (Attenuation). هذا القيد الفيزيائي الدقيق هو المكان الذي أسست فيه شركات تصميم أشباه الموصلات النخبوية والمتخصصة بشدة—أبرزها شركة Astera Labs المفضلة في الصناعة والتكتل المخضرم Microchip Technology—احتكارات شبه كاملة راسخة، محققة إيرادات مالية أسطورية وفلكية طوال عام 2026 من خلال التصنيع الحصري وتوزيع رقائق دقيقة فائقة التخصص تُصنف رسمياً باسم "مؤقتات إعادة البيانات" (Data Retimers).

تعمل شريحة Retimer بشكل أساسي كـ "محطة تقوية وإعادة بناء رقمية للإشارة" يتم تثبيتها فعلياً وبشكل مباشر على خط المنتصف لكابلات ربط PCIe الشاسعة التي تجسر بين مكونات الخادم الداخلية. هذه الشريحة شديدة التعقيد وباهظة الثمن تقوم فعلياً باعتراض موجة إشارة PAM4 المشوهة بشدة والمكدومة والمتدهورة للغاية في منتصف رحلتها المؤلمة عبر الأسلاك النحاسية. تقوم بتطهير الشكل الموجي الفوضوي بعنف باستخدام منطق معالجة الإشارات الرقمية (DSP) العميق، وتجرد تماماً كل ضوضاء الترددات الراديوية (RF) الخلفية المتراكمة، ثم تعيد بناء وتوليد موجة إشارة رقمية أصلية وصافية تماماً كالمرايا وبلا عيوب. بعد ذلك، تقوم بعرض هذه الإشارة المعاد بناؤها بإتقان إلى الأمام لتمتلك نفس القوة الهيكلية الأصلية نحو وجهة معالجتها النهائية ولولا هذه الشرائح المتقدمة بحجم 3 و 5 نانومتر لما أمكن تشغيل أي معمارية ذكاء اصطناعي حديثة ومشتتة.

القسم السادس: التأثير المباشر على مسرعات الذكاء الاصطناعي (Nvidia B200 و AMD MI400)

يعتمد الإطلاق العالمي شديد الانفجار للجيل القادم من "حوامل مشغلي الذكاء الاصطناعي" (AI Supervisor Racks) الذي ضرب سوق الشركات الثقيلة فعلياً في النصف الثاني الحاسم من عام 2026—والذي تقوده بشراسة عمليات Nvidia الرائدة—بشكل كامل على الوجود الأساسي لمنافذ واجهة PCIe 6.0 المتصلة مباشرة. لتجميع وتدريب بنية لغوية أساسية تنافس بنجاح وبقوة حجم بنية نظرية مثل GPT-5، لا يمكن لمهندسي الأجهزة إطلاقاً الاعتماد فقط على جسور متخصصة ومملوكة مثل ارتباطات NVLink من Nvidia. بل فرضوا بشكل عاجل وعدواني استخدام بطاقات جسر شبكات قياسية وسريعة بشكل جنوني (مثل وحدات تحكم إيثرنت 800-Gigabit أو 1.6-Terabit) ومصفوفات موسعة بفضل محركات تخزين NVMe فائقة السرعة المستمرة لـ "تغذية" نوى المعالج الرسومي فائقة الجوع ببيانات التدريب الخام بشكل فوري تقريباً وبلا هوادة.

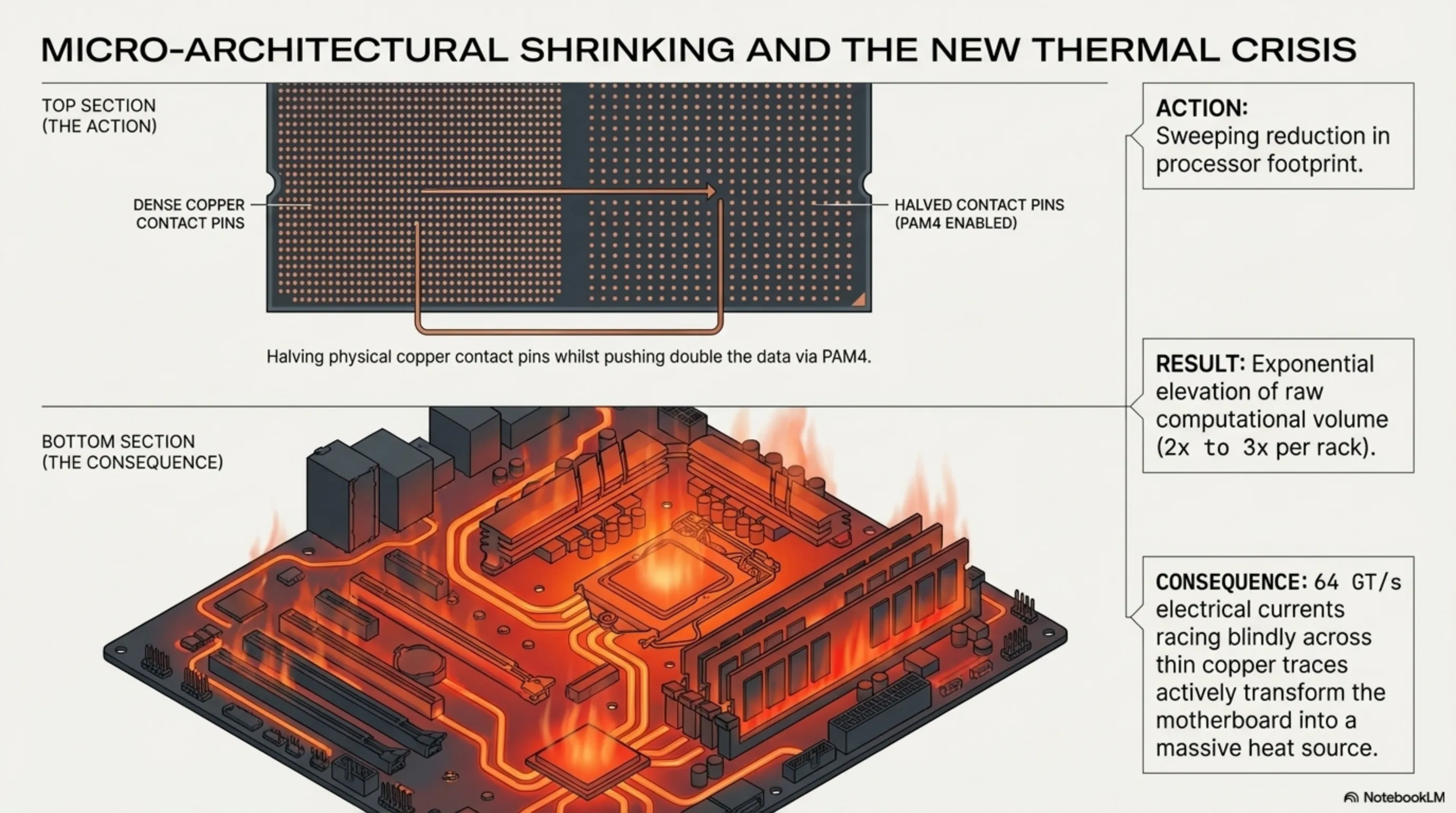

منحت هذه الهجرة المنهجية على مستوى الصناعة بأكملها للغوص العميق في إطار PCIe Gen 6 لمهندسي تصميم السيليكون النخبة قدرة فيزيائية سحرية وعملية ومهيبة: فبدلاً من الحاجة الأساسية لبناء دبابيس تلامس فيزيائية ضخمة وموزعة على نطاق واسع عبر قالب المعالج لنقل البيانات الثقيلة، تمكنوا من خفض عدد الدبابيس النحاسية المادية إلى النصف بقوة، مع استغلال معمارية PAM4 المزدحمة بشدة لدفع ضعف كمية البيانات عبر تلك البصمة المصغرة. أدت هذه الاستراتيجية الميكرو-معمارية العميقة للغاية والعدوانية فوراً وبشكل حاسم إلى الانكماش المادي العميق لبصمة المعالج المركزي (CPU) والرسومي (GPU) على اللوحة الأم، مما أدى بنجاح إلى تحفيز انخفاض شامل وهائل في توليد الحرارة الموضعية الكلية المحيطة عبر منشآت الخوادم السحابية الضخمة، مع الحفاظ بسلاسة تامة على السعة الوحشية لرفع الحجم الحسابي الخام لكل حامل خادم واحد في مركز البيانات الحديث بشكل هائل ومضاعف بمقدار مرتين إلى ثلاث مرات.

القسم السابع: ميكانيكا التبريد: التبديد الحراري في البيئات الدقيقة بسرعة 64 GT/s

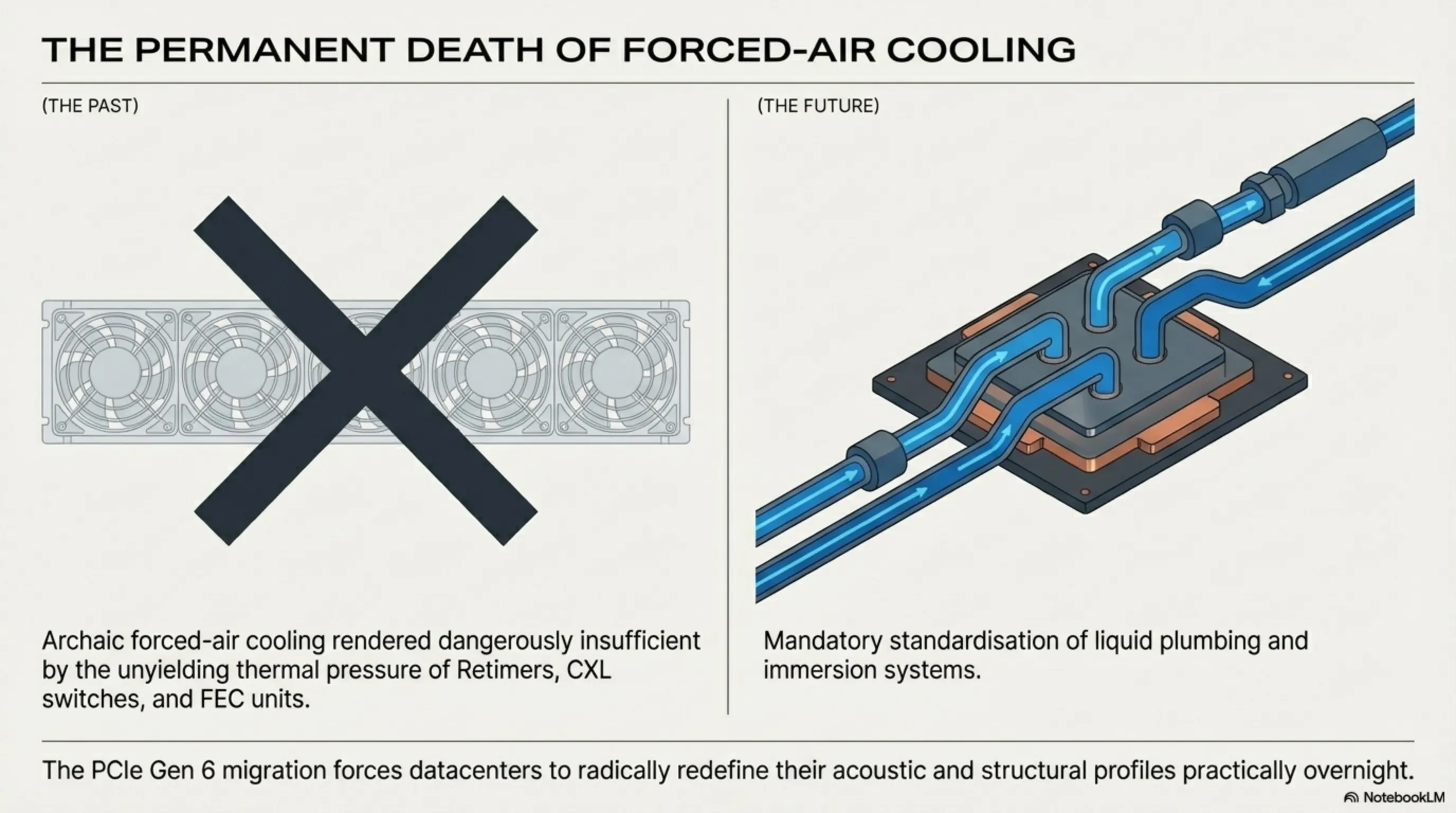

من بين العواقب التي طالما تم تحليلها بشكل أقل من حجمها بكثير وتجاهلها بشدة، والتي نتجت مباشرة عن الدمج العنيف لأنظمة PCIe 6.0 في الحواسيب المركزية (Mainframes)، تبرز الأزمة الهندسية المعقدة والمرعبة المحيطة بديناميكيات الحرارة الموضعية. فبينما قد تكون المعالجات التكنولوجية نفسها قلصت من دبابيس الاتصال الفيزيائية بنجاح، فإن التدفق الهائل والعنيف لتيارات كهربائية بتردد 64 GT/s تتسابق بشكل أعمى وسريع عبر المسارات النحاسية الرقيقة للوحة الدوائر المطبوعة (PCB) يحول اللوحة المادية نفسها باستمرار إلى مشعاع حراري (Radiator) ضخم ومشدود الحرارة بشكل مكثف. تتكدس شرائح Retimer المتخصصة، ومصفوفات تبديل CXL 3.2 الثقيلة، ووحدات حساب FEC المدمجة بعمق—والتي تعمل جميعها باستمرار وبأقصى حمل ممكن—وتولد مستويات مكثفة ومخيفة من الإشعاع الحراري المتراكم بحدة.

لقد جعل هذا الضغط الحراري المستمر وأنظمة مروحة تبريد الهواء القسري الكلاسيكية والتقليدية والقديمة بالية تماماً وغير كافية بشكل خطير وتهديدي لهذه المناطق المحددة وعالية الكثافة. وبالتالي، أدى التبني الهائل والمطلق لـ PCIe Gen 6 مباشرة وفي نفس الوقت وبقوة إلى إجبار بيئة مركز البيانات على التخلي الكامل والنهائي عن المراوح والتوحيد العنيف حول معمارية التبريد السائل المباشر للرقاقة (Direct-to-Chip Liquid Cooling - DLC) وحلول التبريد الغمري (Immersion Cooling) العميقة والكبيرة بين عشية وضحاها تقريباً، وهو ما أعاد تحديد شكل وتصميم ومظهر السباكة والملف الصوتي لمراكز معالجة وتخزين البيانات الحديثة بالكامل.

القسم الثامن: سلاسل التوريد العالمية: الكابلات البصرية النشطة (AOC) وتكلفة موت النحاس

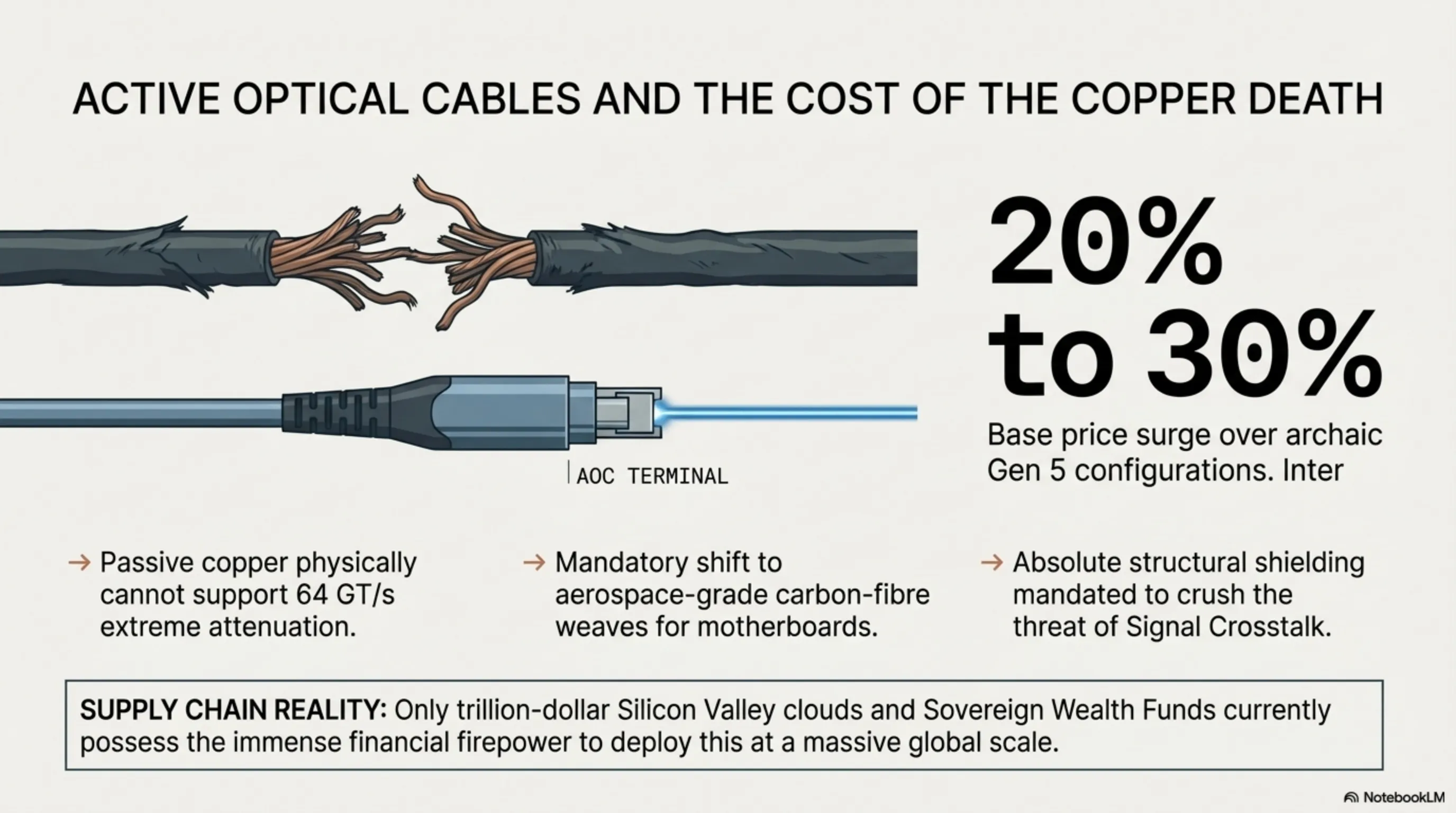

من منظور اقتصادي صارم وقاسٍ جداً، يمثل الانتقال نحو طوبولوجيا PCIe 6.0 دورة إنفاق قوية ومكلفة للغاية وعنيفة للغاية للبنية التحتية للمؤسسات. لقد فشلت كابلات النحاس السلبية (Passive Copper Cabling) القياسية والرخيصة للغاية، والتي كانت تُستخدم سابقًا بأطوال هائلة ومذهلة لربط حوامل الخوادم، فشلاً ذريعاً وانهارت تماماً؛ فهي لا تستطيع فعلياً ومادياً دعم متطلبات التوهين والتخميد (Attenuation) القصوى لموجة الإشارة الجديدة دون إتلاف وتدمير البيانات. ونتيجة لذلك، يجب انتزاع وتمزيق جميع الوصلات الطويلة الممتدة داخل مركز البيانات الحديث تقريباً بشكل عنيف واستبدالها فوراً بكابلات بصرية نشطة (Active Optical Cables - AOC) مكلفة بشكل جنوني ومعقدة للغاية وأغلى سعرا، والتي تترجم فعلياً الإشارة الكهربائية إلى ضوء نقي ومثالي باستخدام ليزر مدمج في كل محطة اتصال فيزيائية ونهائية.

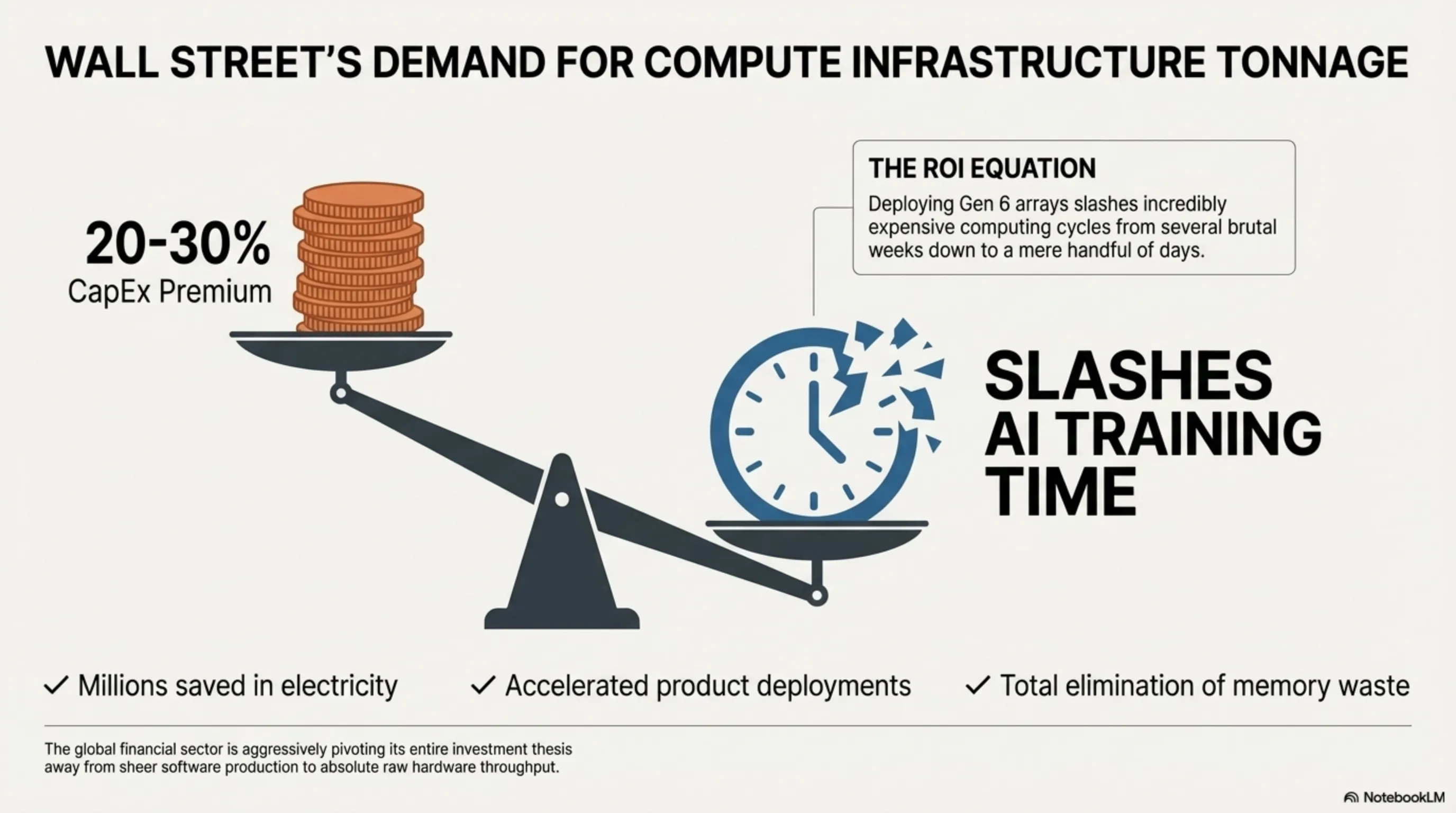

وعلاوة على ذلك، فإن المطالبة بالاستخدام الحصري للوحات أم متطورة بشكل مذهل وللوحات صُممت بدقة متناهية مع نسج من ألياف الكربون المستخدمة في مجال الطيران وتحقيق العزل التام والمطلق (Shielding) لسحق تهديد تداخل الإشارات (Crosstalk) بشكل عدواني يؤدي إلى تضخم السعر الأساسي لخادم الدعامة المعدني (Bare-Metal Server) بنسبة مذهلة تتراوح من 20 إلى 30 بالمائة عند مقارنتها تاريخياً وتجارياً مع تكوينات خوادم الجيل الخامس الأقدم. تملي هذه الطفرة الهائلة والعنيفة في النفقات الرأسمالية الهيكلية المطلوبة بشدة أن فقط الدول والمؤسسات الأكثر ثراءً وإمكانيات، وصناديق الثروة السيادية العميقة جداً، والمشاريع السعودية الضخمة (مثل مشروع نيوم)، وسحابات وادي السيليكون التريليونية التي تمتلك القوة المالية الهائلة التي لا يمكن تصورها، هي التي تمتلك وتتمكن من شراء ونشر هذه المصفوفات والمقاسم العالمية الكبيرة من CXL 3.2 بشكل مكثف وعلى نطاق واسع في العالم أجمع.

القسم التاسع: تأثير ذلك على مراكز بيانات الشرق الأوسط: نيوم ودبي ومستقبل الحوسبة السحابية الخليجية

يتمتع الشرق الأوسط بموقع فريد واستراتيجي في خضم هذه الثورة التحتية الضخمة. فمشاريع مراكز البيانات العملاقة في المنطقة - من مدينة نيوم الذكية في المملكة العربية السعودية والتي تمثل رؤية 2030 بكل قوتها واستثماراتها الهائلة التي لا حدود لها ولا سقف لميزانيتها، إلى مراكز بيانات مايكروسوفت وأوراكل وأمازون ويب سيرفيسز (AWS) المتوسعة بسرعة هائلة في دبي وأبوظبي والدوحة والرياض - جميعها تتنافس بشراسة منقطعة النظير على أن تكون المحور الإقليمي الأول والأكبر لتدريب ونشر نماذج الذكاء الاصطناعي الثقيلة والضخمة.

ولتحقيق هذا الطموح المتوقد بالمال والتخطيط والإرادة السياسية الحديدية الخليجية، فإن الاعتماد على بنية PCIe 5.0 القديمة والمتقادمة سيكون وبكل بساطة ووضوح انتحاراً تقنياً واستراتيجياً محضاً ومكلفاً للغاية. إن سعات الطاقة الكهربائية الضخمة المتوفرة في دول الخليج العربي بفضل احتياطيات النفط والغاز الهائلة توفر ميزة تنافسية فريدة لتشغيل مراكز البيانات الفائقة، ولكن الاستفادة الحقيقية من هذه الطاقة لن تتحقق إلا عبر تبني معمارية PCIe 6.0 و CXL 3.2 التي تقلل الهدر وتضاعف الأداء الحوسبي لكل واط مستهلك.

تشير التقارير الصناعية المتخصصة من DigiTimes و Bloomberg إلى أن صناديق الثروة السيادية في عدة دول خليجية وضعت طلبيات مبكرة وعقوداً استباقية تقدر بمئات الملايين من الدولارات لاستيراد ونشر أول دفعات من خوادم PCIe 6.0 المجهزة بمحولات CXL 3.2 في الربع الرابع من عام 2026 والنصف الأول من عام 2027. هذه الاستثمارات الاستباقية الضخمة تهدف بوضوح إلى وضع المنطقة في مقدمة سباق الذكاء الاصطناعي العالمي، وتحويل منطقة الخليج من مستهلك تقليدي للتكنولوجيا إلى منتج ومصدر للابتكار الحوسبي والذكاء الاصطناعي التوليدي على مستوى العالم بأسره.

القسم العاشر: هندسة الأمان: سلامة البيانات وتشفيرها عبر الكابلات البينية

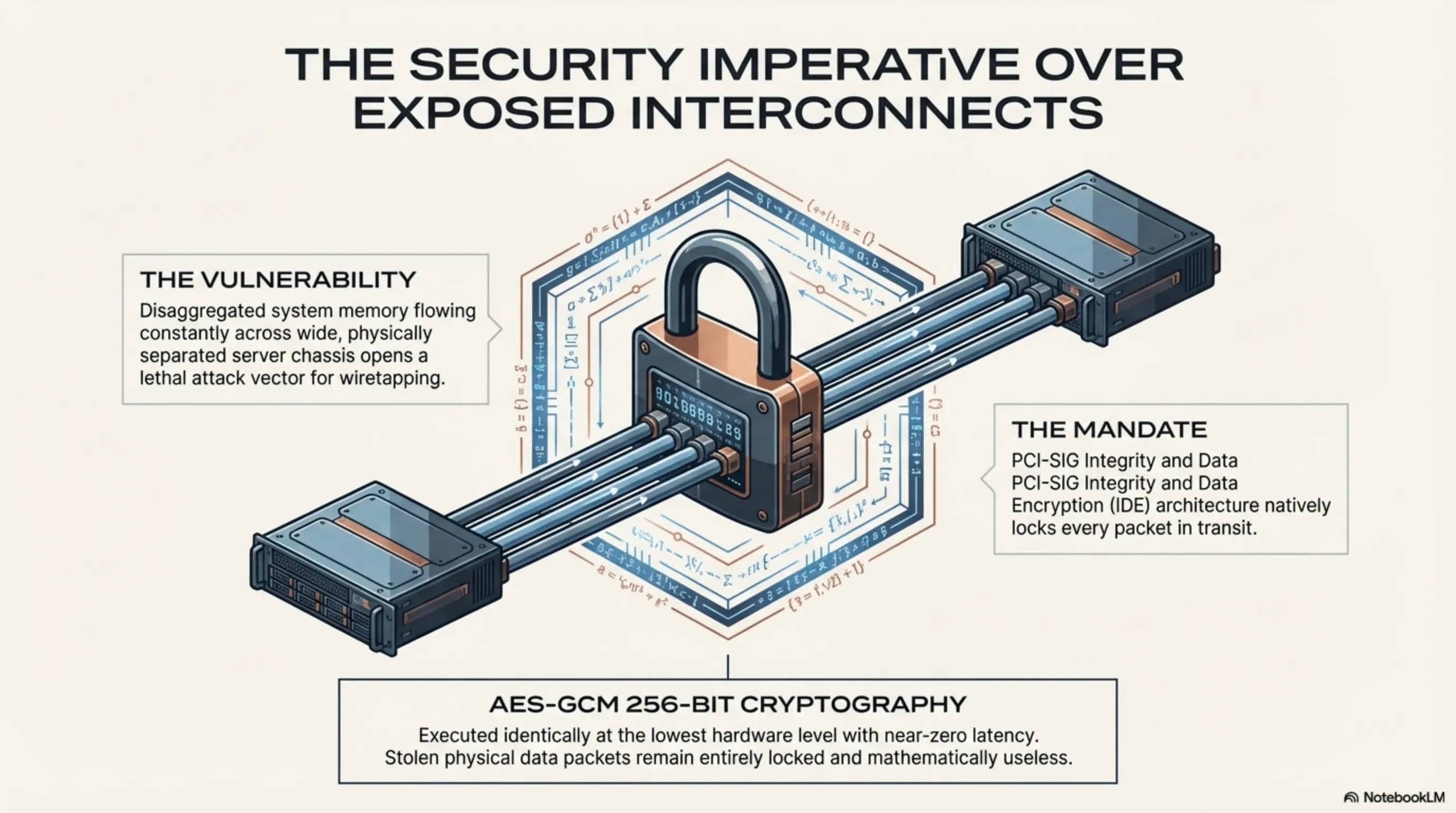

مع التحول السريع والعدواني لمراكز البيانات بالكامل نحو إطار العمل المفكك كلياً والذي يفرضه بروتوكول CXL 3.2، انفتح ناقل هجوم أمني جديد ضخم ومميت للغاية. ونظراً لأن بيانات ذاكرة النظام شديدة الأهمية وشديدة الحساسية (وغير المشفرة مسبقًا) تتدفق الآن باستمرار وبسرعة فائقة عبر كابلات مادية مكشوفة وواسعة تصل بين هياكل خوادم منفصلة جسدياً تماماً، فقد تم اختراق مفهوم الأمان المحلي كلياً. يمكن لمخترق خبيث عالي التطور، أو وحدة تجسس مؤسسية النخبة، نظرياً اعتراض تدفقات البيانات الضخمة هذه دون أن يلاحظها أحد تقريباً، من خلال تنفيذ عمليات تنصت مادي هجومية مباشرة على روابط الاتصال بين الخوادم.

للتصدي بلا رحمة وتدمير هذا التهديد الداخلي الشديد، قامت مؤسسة PCI-SIG بدمج معمارية "سلامة وتشفير البيانات" (IDE - Integrity and Data Encryption) شديدة الصرامة مباشرة في الأساس الجوهري لبروتوكولات PCIe 6.0 و CXL 3.x الموحدة. مدفوعة بشكل أساسي بتقنية التشفير العميق AES-GCM 256-bit والمنفذة بشكل متطابق في أدنى مستوى من الأجهزة ضمن نقاط الاتصال النهائية وبكمون شبه معدوم، يتم تشفير ومصادقة كل جزيء من حزم البيانات التي تعبر حوامل الخوادم حرفياً ومطلقاً. هذا يعني أنه حتى لو نجح المهاجم في اختراق المحيط الأمني المشدد لمركز بيانات من الدرجة الحكومية وربط أجهزة تنصت مباشرة بالخوادم، فستبقى رزم البيانات المسروقة مغلقة بالكامل، ومقيدة بتشفير ثقيل، وبلا أي فائدة رياضية للمهاجم، مما يضمن تماماً سلامة هياكل الحوسبة اللامركزية للذكاء الاصطناعي على مستوى العالم.

القسم الحادي عشر: الخاتمة الهيكلية: الشرط الأساسي الحتمي لعصر التريليون معامل

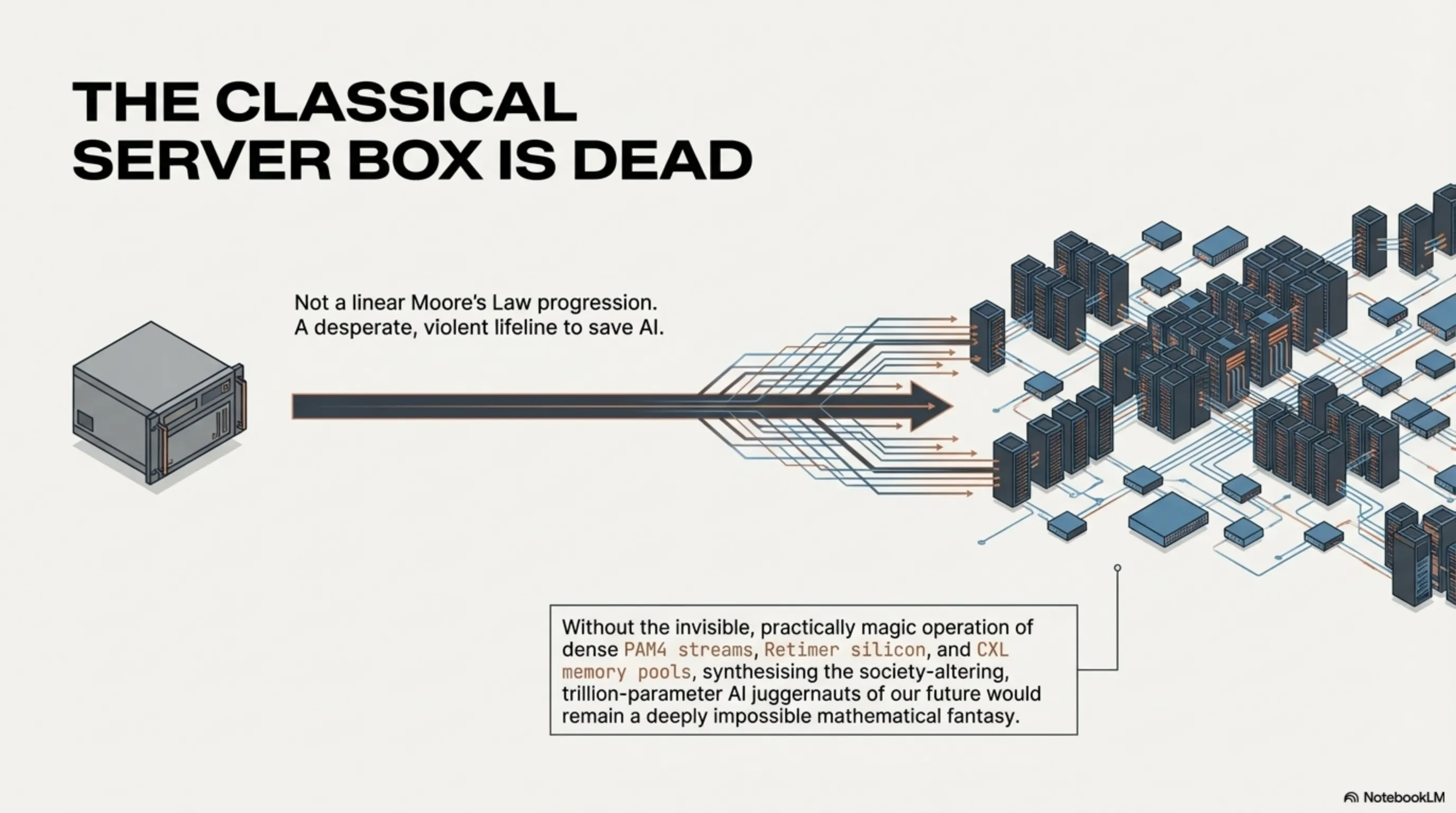

في التحليل النهائي الصادق بقسوة والمدقق بشدة، فإن الهجرة الصناعية الهائلة والمفروضة بقوة باتجاه القوة المذهلة لمعيار PCIe Gen 6 - ومعياره المرافق والمحول والمدمر للأنظمة بشكل عميق CXL 3.2 - لا تمثل بشكل حاسم ومطلق مجرد تقدم تطوري خطي ومتوقع ومعتاد للأجهزة يتماشى تماما ومتناغماً مع المسار المنتظم لقانون مور المعتاد والمتوقع والروتيني. بل تمثل شيئاً أعمق وأخطر بكثير: إنها شريان الحياة اليائس والعنيف بشكل لا يصدق والاستراتيجية الوحيدة المنقذة لقطاع السيليكون العالمي لتجنب التوقف الكلي والكارثي المطلق فيما يتعلق بالتقدم المستمر للذكاء الاصطناعي.

من خلال التخلي بشراسة ونجاح عن البنية القديمة المقيدة جوهرياً لأنظمة الإرسال ثنائية الحالة وتطبيق إشارات PAM4 الكثيفة ببراعة، إلى جانب مجمعات ذاكرة CXL الديناميكية والمتدفقة بثقل والممتدة هيكلياً عبر منشآت ضخمة واسعة، فقد توقف الخادم الكلاسيكي عملياً عن الوجود كصندوق معزول وصلب. لقد تحول بشكل عدواني إلى دماغ مترابط بالكامل وموزع بشكل رائع، ينقل بسلاسة سيولاً لا يمكن تصورها من البيانات الحرجة بعمق تحت السطح.

الحكم التحريري النهائي من مكتب هندسة Tekin: المخرج الوحيد من الاختناق الكارثي لعرض النطاق الترددي

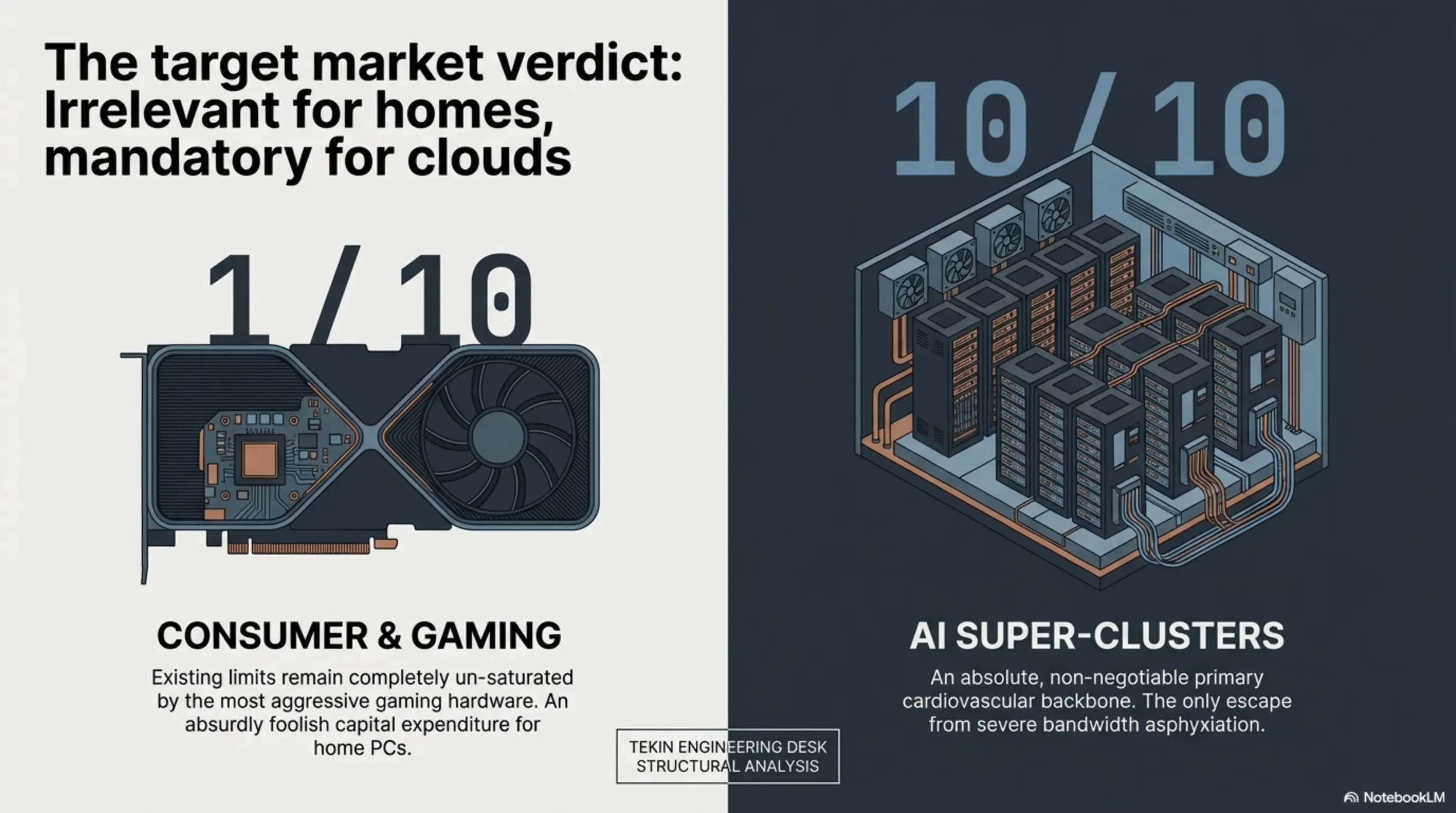

قيمة الأجهزة للحوسبة المنزلية والألعاب والمستهلكين العاديين: 1 من 10 (تظل حدود عرض النطاق الترددي لأنظمة PCIe 4.0 و PCIe 5.0 غير مشبعة تماماً حتى من قبل أقوى بطاقات الرسومات المخصصة للألعاب المتاحة حالياً في السوق بما فيها RTX 5090. وبالتالي فإن الاستثمار في هذه البنية للاستخدام المنزلي البحت يمثل إنفاقاً سخيفاً وغير عقلاني.)

ضرورة حاسمة لمنصات السحابة العالمية ومجموعات الذكاء الاصطناعي الفائقة: 10 من 10 (هذه الطوبولوجيا تعمل حصرياً كالعمود الفقري القلبي الوعائي المطلق وغير القابل للتفاوض المطلوب لمجرد إبقاء أجهزة مسرعات الذكاء الاصطناعي النهمة من الجيل التالي حية وعاملة بقوة دون أن تنهار على نفسها تماماً.)

التحليل الاستراتيجي النهائي من Tekin: إن البنية المحددة لـ PCIe Gen 6.0 وآليتها الشاملة الرائعة CXL 3.2 ليست ترقيات جيلية روتينية ومملة. إنشاؤها المعقد للغاية وظهورها المتسارع في السوق يمثل في الواقع الاعتراف العميق والصادق بفشل سختافزاري شدید! صناعة السيليكون العالمية عند وصولها بعنف إلى الحد المادي المطلق لمنهجية NRZ اعترفت أخيراً أن آثار النحاس الخام لا يمكنها رياضياً تحمل ترددات أعلى. هذا الانتقال الضخم يقدم دليلاً لا يقبل الدحض على أن الخوادم الكلاسيكية تتحول إلى دماغ رقمي ضخم مترابط وموزع بالكامل. وللمنطقة العربية والخليجية تحديداً، هذه ليست فقط ترقية تقنية بل هي تذكرة الدخول الإلزامية إلى عصر التريليون معامل.

معرض هندسة مراكز البيانات المتخصصة